### **GLOBAL SERIAL INTERFACE DIRECT ACCESS ARRANGEMENT**

Pulse dialing support

Overload detection

3.3 V power supply

>5000 V isolation

end echo reduction

Direct interface to DSPs

Serial interface control for up to eight

Programmable digital hybrid for near-

Lead-free/RoHS-compliant packages

Proprietary isolation technology

Parallel handset detection

+3.2 dBm TX/RX level mode

Low-profile SOIC packages

#### Features

Complete DAA includes the following:

- Programmable line interfaceAC termination

- AC termination

DC termination

- DC termination

Dirac data at three

- Ring detect threshold

- Ringer impedance

- 80 dB dynamic range TX/RX paths

- Integrated codec and 2- to 4-wire

- hybrid

- Integrated ring detector

- Type I and II caller ID support

- Line voltage monitor

- Loop current monitor

- Polarity reversal detection

- Programmable digital gain

- Clock generation

### Applications

- V.92 modems Set-top boxes

- Voice mail systems Fax machines

- Multi-function printers

- Internet appliances

Personal digital

- Personal digital assistants

### Description

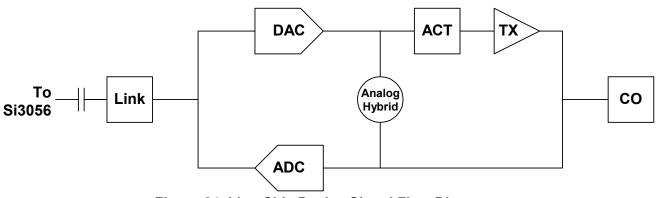

The Si3056 is an integrated direct access arrangement (DAA) with a programmable line interface to meet global telephone line requirements. Available in two 16-pin small outline packages, it eliminates the need for an analog front end (AFE), isolation transformer, relays, opto-isolators, and a 2- to 4-wire hybrid. The Si3056 dramatically reduces the number of discrete components and cost required to achieve compliance with global regulatory requirements. The Si3056 interfaces directly to standard modem DSPs.

devices

available

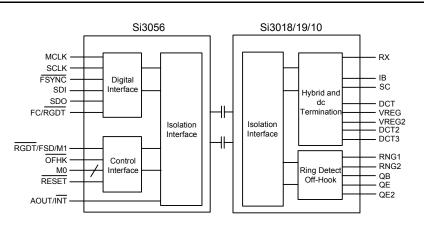

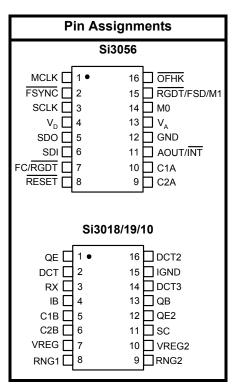

### **Functional Block Diagram**

US Patent # 5,870,046 US Patent # 6,061,009 Other Patents Pending

Rev. 1.05 6/05

## TABLE OF CONTENTS

| Section Pa                                                     | <u>ge</u> |

|----------------------------------------------------------------|-----------|

| 1. Electrical Specifications                                   |           |

| 2. Typical Application Schematic                               | .18       |

| 3. Bill of Materials                                           |           |

| 4. AOUT PWM Output                                             | .20       |

| 5. Functional Description                                      |           |

| 5.1. Upgrading from the Si3034/35/44 to Si3056                 |           |

| 5.2. Line-Side Device Support                                  |           |

| 5.3. Power Supplies                                            |           |

| 5.4. Initialization                                            |           |

| 5.5. Isolation Barrier                                         |           |

| 5.6. Transmit/Receive Full Scale Level (Si3019 Line-Side Only) |           |

| 5.7. Parallel Handset Detection                                |           |

| 5.8. Line Voltage/Loop Current Sensing                         |           |

| 5.9. Off-Hook                                                  |           |

| 5.10. Interrupts                                               |           |

| 5.11. DC Termination                                           |           |

| 5.12. AC Termination                                           |           |

| 5.13. Transhybrid Balance                                      |           |

| 5.14. Ring Detection                                           |           |

| 5.15. Ring Validation                                          |           |

| 5.16. Ringer Impedance and Threshold                           |           |

| 5.17. Pulse Dialing and Spark Quenching                        |           |

| 5.18. Billing Tone Protection and Receive Overload             |           |

| 5.19. Billing Tone Filter (Optional)                           |           |

| 5.20. On-Hook Line Monitor                                     |           |

| 5.21. Caller ID                                                | . 32      |

| 5.22. Overload Detection                                       | .35       |

| 5.23. Gain Control                                             | .35       |

| 5.24. Filter Selection                                         | .36       |

| 5.25. Clock Generation                                         | .36       |

| 5.26. Digital Interface                                        | .37       |

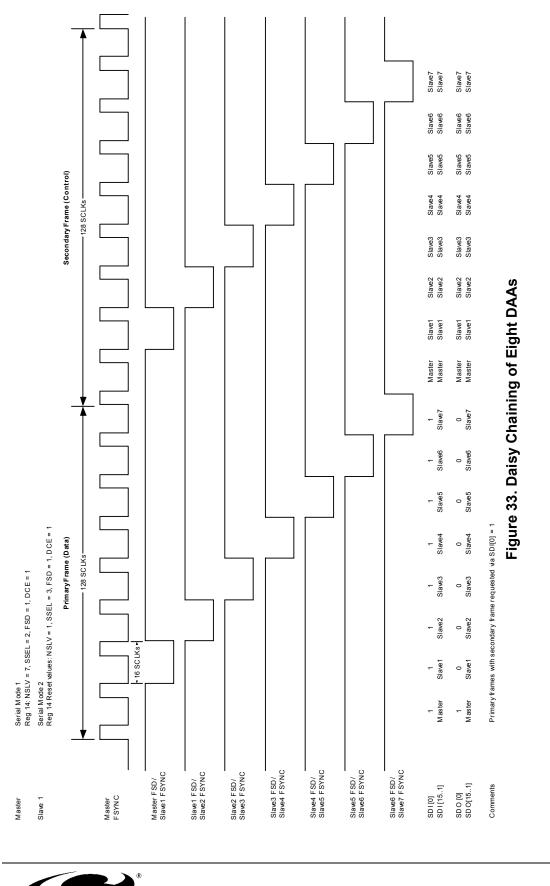

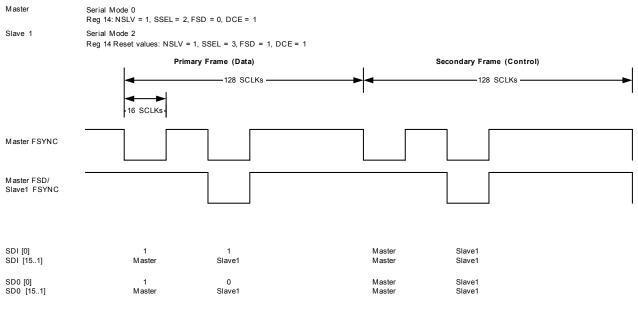

| 5.27. Multiple Device Support                                  | . 38      |

| 5.28. Power Management                                         | . 39      |

| 5.29. Calibration                                              |           |

| 5.30. In-Circuit Testing                                       | . 39      |

| 5.31. Exception Handling                                       |           |

| 5.32. Revision Identification                                  | .40       |

| 6. Control Registers                                           | .48       |

| Appendix—UL1950 3rd Edition                                    | .83       |

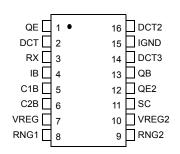

| 7. Pin Descriptions: Si3056                                    | .84       |

| 8. Pin Descriptions: Si3018/19/10                              | .86       |

| 9. Ordering Guide                                 | 8 |

|---------------------------------------------------|---|

| 10. Evaluation Board Ordering Guide               | 9 |

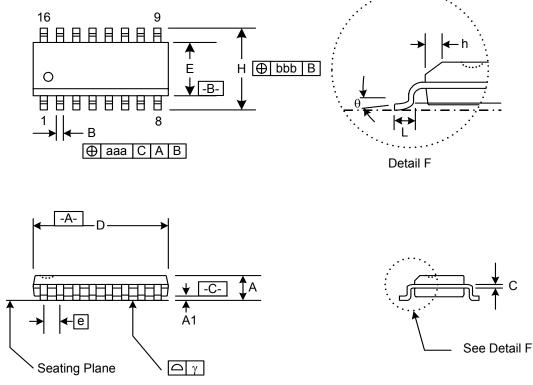

| 11. Package Outline: 16-Pin SOIC                  | 0 |

| Document Change List                              | 1 |

| Silicon Laboratories Si3056 Support Documentation | 3 |

| Contact Information                               |   |

### 1. Electrical Specifications

### **Table 1. Recommended Operating Conditions**

| Parameter <sup>1</sup>                                                                                                            | Symbol         | Test Condition | Min <sup>2</sup> | Тур | Max <sup>2</sup> | Unit |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|------------------|-----|------------------|------|--|--|

| Ambient Temperature                                                                                                               | T <sub>A</sub> | F and K-Grade  | 0                | 25  | 70               | °C   |  |  |

| Si3056 Supply Voltage, Digital <sup>3</sup>                                                                                       | V <sub>D</sub> |                | 3.0              | 3.3 | 3.6              | V    |  |  |

| Notes:<br>1 The Si3056 specifications are guaranteed when the typical application circuit (including component tolerance) and the |                |                |                  |     |                  |      |  |  |

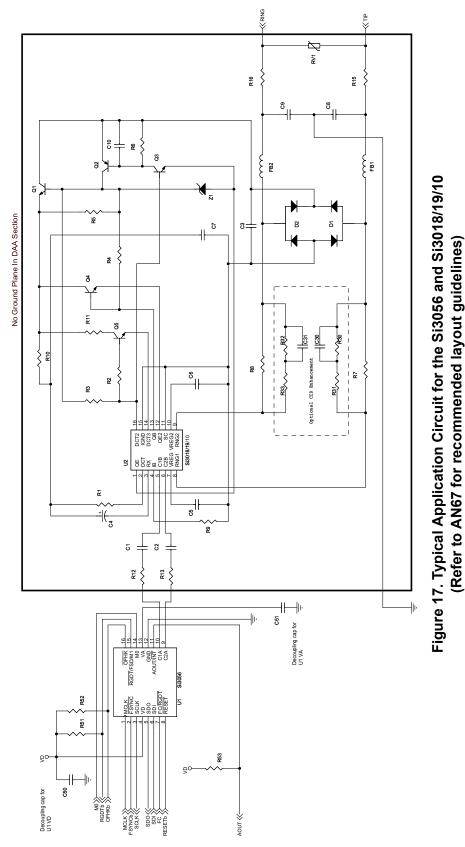

The Si3056 specifications are guaranteed when the typical application circuit (including component tolerance) and the Si3056 and any Si3018 or Si3019 are used. See Figure 17 on page 18 for typical application schematic.

2. All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions.

Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise stated.

3. 3.3 V applies to both the digital and serial interface and the digital signals RGDT/FSD, OFHK, RESET, M0, and M.

### **Table 2. Loop Characteristics**

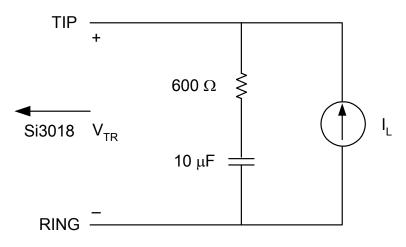

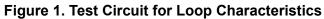

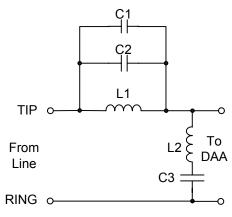

(V<sub>D</sub> = 3.0 to 3.6 V,  $T_A$  = 0 to 70 °C, see Figure 1)

| Parameter                 | Symbol          | Test Condition                                                     | Min   | Тур  | Мах   | Unit             |

|---------------------------|-----------------|--------------------------------------------------------------------|-------|------|-------|------------------|

| DC Termination Voltage    | V <sub>TR</sub> | I <sub>L</sub> = 20 mA, MINI = 11,<br>ILIM = 0, DCV = 00, DCR = 0  | _     | _    | 6.0   | V                |

| DC Termination Voltage    | V <sub>TR</sub> | I <sub>L</sub> = 120 mA, MINI = 11,<br>ILIM = 0, DCV = 00, DCR = 0 | 9     | —    | —     | V                |

| DC Termination Voltage    | V <sub>TR</sub> | I <sub>L</sub> = 20 mA, MINI = 00,<br>ILIM = 0, DCV = 11, DCR = 0  | _     |      | 7.5   | V                |

| DC Termination Voltage    | V <sub>TR</sub> | I <sub>L</sub> = 120 mA, MINI = 00,<br>ILIM = 0, DCV = 11, DCR = 0 | 9     | —    | —     | V                |

| DC Termination Voltage    | V <sub>TR</sub> | I <sub>L</sub> = 20 mA, MINI = 00,<br>ILIM = 1, DCV = 11, DCR = 0  | —     | —    | 7.5   | V                |

| DC Termination Voltage    | V <sub>TR</sub> | I <sub>L</sub> = 60 mA, MINI = 00,<br>ILIM = 1, DCV = 11, DCR = 0  | 40    | —    | —     | V                |

| DC Termination Voltage    | V <sub>TR</sub> | I <sub>L</sub> = 50 mA, MINI = 00,<br>ILIM = 1, DCV = 11, DCR = 0  | _     | —    | 40    | V                |

| On Hook Leakage Current   | I <sub>LK</sub> | V <sub>TR</sub> = -48 V                                            | _     | _    | 5     | μA               |

| Operating Loop Current    | I <sub>LP</sub> | MINI = 00, ILIM = 0                                                | 10    | _    | 120   | mA               |

| Operating Loop Current    | I <sub>LP</sub> | MINI = 00, ILIM = 1                                                | 10    |      | 60    | mA               |

| DC Ring Current           |                 | DC current flowing through ring detection circuitry                |       | 1.5  | 3     | μA               |

| Ring Detect Voltage*      | V <sub>RD</sub> | RT = 0                                                             | 13.5  | 15   | 16.5  | V <sub>rms</sub> |

| Ring Detect Voltage*      | V <sub>RD</sub> | RT = 1                                                             | 19.35 | 21.5 | 23.65 | V <sub>rms</sub> |

| Ring Frequency            | F <sub>R</sub>  |                                                                    | 13    |      | 68    | Hz               |

| Ringer Equivalence Number | REN             |                                                                    |       |      | 0.2   |                  |

### Table 3. DC Characteristics, $V_D = 3.3 V$

(V<sub>D</sub> = 3.0 to 3.6 V, T<sub>A</sub> = 0 to 70 °C)

| Parameter                                                    | Symbol          | Test Condition              | Min         | Тур         | Max      | Unit     |

|--------------------------------------------------------------|-----------------|-----------------------------|-------------|-------------|----------|----------|

| High Level Input Voltage                                     | V <sub>IH</sub> |                             | 2.4         | _           | _        | V        |

| Low Level Input Voltage                                      | V <sub>IL</sub> |                             |             |             | 0.8      | V        |

| High Level Output Voltage                                    | V <sub>OH</sub> | I <sub>O</sub> = –2 mA      | 2.4         | _           |          | V        |

| Low Level Output Voltage                                     | V <sub>OL</sub> | I <sub>O</sub> = 2 mA       |             | _           | 0.35     | V        |

| Input Leakage Current                                        | ΙL              |                             | -10         | _           | 10       | μA       |

| Power Supply Current, Digital <sup>1</sup>                   | I <sub>D</sub>  | V <sub>D</sub> pin          |             | 15          |          | mA       |

| Total Supply Current, Sleep Mode <sup>1</sup>                | I <sub>D</sub>  | PDN = 1, PDL = 0            |             | 9           |          | mA       |

| Total Supply Current, Deep Sleep <sup>1,2</sup>              | I <sub>D</sub>  | PDN = 1, PDL = 1            |             | 1           |          | mA       |

| Notes:<br>1. All inputs at 0.4 or V <sub>D</sub> – 0.4 (CMOS | levels). All in | puts are held static except | clock and a | all outputs | unloaded | <u> </u> |

$\frac{\text{(Static }I_{OUT} = 0 \text{ mA})}{\text{RGDT is not functional in this state.}}$

#### Table 4. AC Characteristics

(V<sub>D</sub> = 3.0 to 3.6 V,  $T_A$  = 0 to 70 °C; see Figure 17 on page 18)

| Parameter                                            | Symbol            | Test Condition                                                     | Min | Тур    | Мах | Unit              |

|------------------------------------------------------|-------------------|--------------------------------------------------------------------|-----|--------|-----|-------------------|

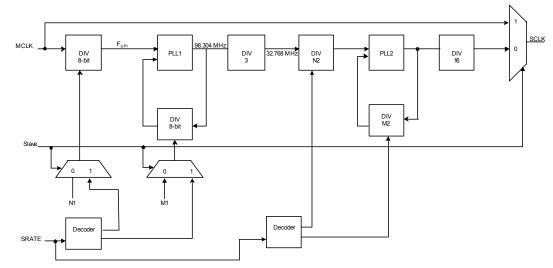

| Sample Rate <sup>1</sup>                             | Fs                | Fs = F <sub>PLL2</sub> /5120                                       | 7.2 | —      | 16  | kHz               |

| PLL Output Clock Frequency <sup>1</sup>              | F <sub>PLL1</sub> | F <sub>PLL1</sub> = (F <sub>MCLK</sub> x M)/N                      | _   | 98.304 | —   | MHz               |

| Transmit Frequency Response                          |                   | Low –3 dBFS Corner                                                 | —   | 0      |     | Hz                |

| Receive Frequency Response                           |                   | Low –3 dBFS Corner,<br>FILT = 0                                    | —   | 5      | —   | Hz                |

| Receive Frequency Response                           |                   | Low –3 dBFS Corner,<br>FILT = 1 <sup>11</sup>                      | _   | 200    | _   | Hz                |

| Transmit Full Scale Level <sup>2,3</sup>             | V <sub>FS</sub>   | FULL = 0 (0 dBm)                                                   | _   | 1.1    | _   | $V_{PEAK}$        |

|                                                      |                   | FULL = 1 <sup>11</sup> (3.2 dBm)                                   | _   | 1.58   |     | $V_{PEAK}$        |

|                                                      |                   | FULL2 = 1 (6.0 dBm)                                                | _   | 2.16   | _   | V <sub>PEAK</sub> |

| Receive Full Scale Level <sup>2,4</sup>              | V <sub>FS</sub>   | FULL = 0 (0 dBm)                                                   |     | 1.1    |     | $V_{PEAK}$        |

|                                                      |                   | FULL = 1 <sup>11</sup> (3.2 dBm)                                   | _   | 1.58   | —   | $V_{PEAK}$        |

|                                                      |                   | FULL2 = 1 (6.0 dBm)                                                | _   | 2.16   | —   | $V_{PEAK}$        |

| Dynamic Range <sup>5,6,7</sup>                       | DR                | ILIM = 0, DCV = 11, DCR = 0,<br>I <sub>L</sub> = 100 mA, MINI = 00 | _   | 80     | _   | dB                |

| Dynamic Range <sup>5,6,7</sup>                       | DR                | ILIM = 0, DCV = 00, DCR = 0,<br>I <sub>L</sub> = 20 mA, MINI = 11  | _   | 80     | _   | dB                |

| Dynamic Range <sup>5,6,7</sup>                       | DR                | ILIM = 1, DCV = 11, DCR = 0,<br>I <sub>L</sub> = 50 mA, MINI = 00  | —   | 80     | _   | dB                |

| Transmit Total Harmonic<br>Distortion <sup>8,9</sup> | THD               | ILIM = 0, DCV = 11, DCR = 0,<br>I <sub>L</sub> = 100 mA, MINI = 00 | —   | -72    | _   | dB                |

| Transmit Total Harmonic<br>Distortion <sup>8,9</sup> | THD               | ILIM = 0, DCV = 00, DCR = 0,<br>I <sub>L</sub> = 20 mA, MINI = 11  | —   | -78    | —   | dB                |

#### Notes:

- 1. See Figure 26 on page 37.

- 2. Measured at TIP and RING with 600  $\Omega$  termination at 1 kHz, as shown in Figure 1.

- 3. With FULL = 1, the transmit and receive full scale level of +3.2 dBm can be achieved with a 600  $\Omega$  ac termination, while the transmit and receive level in dBm varies with reference impedance, the DAA will transmit and receive 1 dBV into all reference impedances in "FULL" mode. With FULL2 = 1, the transmit and receive full scale level of +6.0 dBm can be achieved with a 600  $\Omega$  ac termination. In "FULL2" mode, the DAA will transmit and receive +1.5 dBV into all reference impedances.

- 4. Receive full scale level produces -0.9 dBFS at SDO.

- DR = 20 x log (RMS V<sub>FS</sub>/RMS V<sub>IN</sub>).+ 20 x log (RMS V<sub>IN</sub>/RMS noise). The RMS noise measurement excludes harmonics. V<sub>FS</sub> is the 0 dBm full-scale level.

- 6. Measurement is 300 to 3400 Hz. Applies to both transmit and receive paths. V<sub>IN</sub> = 1 kHz, -3 dBFS, Fs = 10300 Hz.

- 7. When using the Si3010 line-side, the typical DR values will be approximately 10 dB lower.

- 8. THD = 20 x log (RMS distortion/RMS signal).  $V_{IN}$  = 1 kHz, -3 dBFS, Fs = 10300 Hz.

- 9. When using the Si3010 line-side, the typical THD values will be approximately 10 dB higher.

10. DR<sub>CID</sub> = 20 x log (RMS V<sub>CID</sub>/RMS V<sub>IN</sub>) + 20 x log(RMS V<sub>IN</sub>/RMS noise). V<sub>CID</sub> is the 6 V full-scale level for the typical application circuit in Figure 17. With the enhanced CID circuit, the V<sub>CID</sub> full-scale level is 1.5 V peak, and DR<sub>CID</sub> increases to 62 dB.

**11.** Available on the Si3019 line-side device only.

8

### Table 4. AC Characteristics (Continued)

| Parameter                                           | Symbol            | Test Condition                                                    | Min | Тур | Мах | Unit       |

|-----------------------------------------------------|-------------------|-------------------------------------------------------------------|-----|-----|-----|------------|

| Receive Total Harmonic<br>Distortion <sup>8,9</sup> | THD               | ILIM = 0, DCV = 00, DCR = 0,<br>I <sub>L</sub> = 20 mA, MINI = 11 | _   | -78 |     | dB         |

| Receive Total Harmonic<br>Distortion <sup>8,9</sup> | THD               | ILIM = 1, DCV = 11, DCR = 0,<br>I <sub>L</sub> = 50 mA, MINI = 00 | _   | -78 | _   | dB         |

| Dynamic Range (caller ID<br>mode) <sup>10,7</sup>   | DR <sub>CID</sub> | VIN = 1 kHz, –13 dBFS                                             | —   | 50  | _   | dB         |

| Caller ID Full Scale Level <sup>10</sup>            | V <sub>CID</sub>  |                                                                   | _   | 6   | _   | $V_{PEAK}$ |

| AOUT Low Level Current                              |                   |                                                                   | —   | _   | 10  | mA         |

| AOUT High Level Current                             |                   |                                                                   |     |     | 10  | mA         |

#### Notes:

- 1. See Figure 26 on page 37.

- 2. Measured at TIP and RING with 600  $\Omega$  termination at 1 kHz, as shown in Figure 1.

- 3. With FULL = 1, the transmit and receive full scale level of +3.2 dBm can be achieved with a 600  $\Omega$  ac termination, while the transmit and receive level in dBm varies with reference impedance, the DAA will transmit and receive 1 dBV into all reference impedances in "FULL" mode. With FULL2 = 1, the transmit and receive full scale level of +6.0 dBm can be achieved with a 600  $\Omega$  ac termination. In "FULL2" mode, the DAA will transmit and receive +1.5 dBV into all reference impedances.

- 4. Receive full scale level produces –0.9 dBFS at SDO.

- DR = 20 x log (RMS V<sub>FS</sub>/RMS V<sub>IN</sub>).+ 20 x log (RMS V<sub>IN</sub>/RMS noise). The RMS noise measurement excludes harmonics. V<sub>FS</sub> is the 0 dBm full-scale level.

- 6. Measurement is 300 to 3400 Hz. Applies to both transmit and receive paths. V<sub>IN</sub> = 1 kHz, -3 dBFS, Fs = 10300 Hz.

- 7. When using the Si3010 line-side, the typical DR values will be approximately 10 dB lower.

- 8. THD = 20 x log (RMS distortion/RMS signal).  $V_{IN}$  = 1 kHz, -3 dBFS, Fs = 10300 Hz.

- 9. When using the Si3010 line-side, the typical THD values will be approximately 10 dB higher.

- 10. DR<sub>CID</sub> = 20 x log (RMS V<sub>CID</sub>/RMS V<sub>IN</sub>) + 20 x log(RMS V<sub>IN</sub>/RMS noise). V<sub>CID</sub> is the 6 V full-scale level for the typical application circuit in Figure 17. With the enhanced CID circuit, the V<sub>CID</sub> full-scale level is 1.5 V peak, and DR<sub>CID</sub> increases to 62 dB.

- 11. Available on the Si3019 line-side device only.

### Table 5. Absolute Maximum Ratings

| Symbol           | Value                                                                   | Unit                                                                                 |

|------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| V <sub>D</sub>   | -0.5 to 3.6                                                             | V                                                                                    |

| I <sub>IN</sub>  | ±10                                                                     | mA                                                                                   |

| V <sub>IND</sub> | –0.3 to (V <sub>D</sub> + 0.3)                                          | V                                                                                    |

| T <sub>A</sub>   | -40 to 100                                                              | °C                                                                                   |

| T <sub>STG</sub> | -65 to 150                                                              | °C                                                                                   |

|                  | V <sub>D</sub><br>I <sub>IN</sub><br>V <sub>IND</sub><br>T <sub>A</sub> | $V_D$ -0.5 to 3.6 $I_{IN}$ $\pm 10$ $V_{IND}$ -0.3 to $(V_D + 0.3)$ $T_A$ -40 to 100 |

operation to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods might affect device reliability.

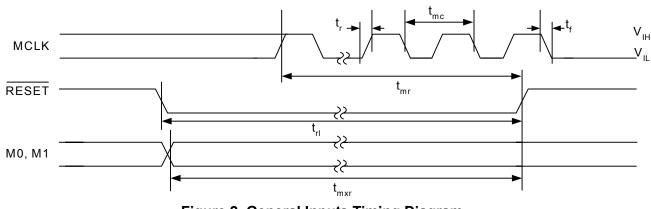

### Table 6. Switching Characteristics—General Inputs

$(V_D = 3.0 \text{ to } 3.6 \text{ V}, T_A = 0 \text{ to } 70 \text{ °C}, C_L = 20 \text{ pF})$

| Parameter <sup>1</sup>           | Symbol              | Min   | Тур | Мах  | Unit   |

|----------------------------------|---------------------|-------|-----|------|--------|

| Cycle Time, MCLK                 | t <sub>mc</sub>     | 16.67 |     | 1000 | ns     |

| MCLK Duty Cycle                  | t <sub>dty</sub>    | 40    | 50  | 60   | %      |

| MCLK Jitter Tolerance            | t <sub>jitter</sub> | —     |     | ±2   | ns     |

| Rise Time, MCLK                  | t <sub>r</sub>      |       |     | 5    | ns     |

| Fall Time, MCLK                  | t <sub>f</sub>      |       |     | 5    | ns     |

| MCLK Before RESET ↑              | t <sub>mr</sub>     | 10    |     | _    | cycles |

| RESET Pulse Width <sup>2</sup>   | t <sub>rl</sub>     | 250   |     | _    | ns     |

| M0, M Before RESET <sup>↑3</sup> | t <sub>mxr</sub>    | 20    |     | _    | ns     |

#### Notes:

1. All timing (except Rise and Fall time) is referenced to the 50% level of the waveform. Input test levels are

$V_{IH} = V_D - 0.4 \text{ V}, V_{IL} = 0.4 \text{ V}$ . Rise and fall times are referenced to the 20% and 80% levels of the waveform. **2.** The minimum RESET pulse width is the greater of 250 ns or 10 MCLK cycle times.

3. M0 and M are typically connected to V<sub>D</sub> or GND and should not be changed during normal operation.

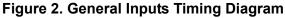

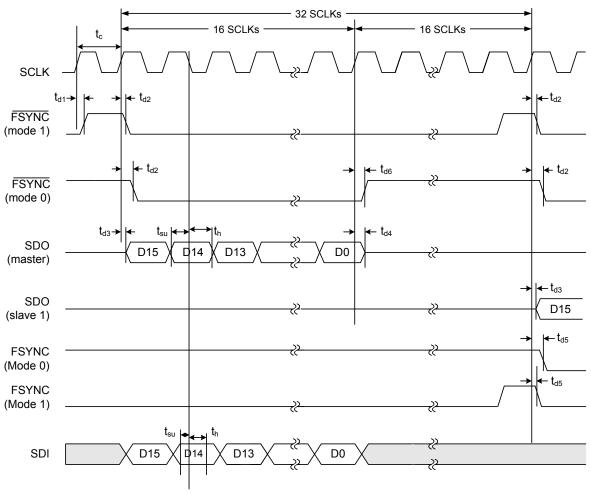

### Table 7. Switching Characteristics—Serial Interface (Master Mode, DCE = 0)

$(V_D = 3.0 \text{ to } 3.6 \text{ V}, T_A = 0 \text{ to } 70 \text{ }^\circ\text{C}, C_L = 20 \text{ pF})$

| Parameter                                          | Symbol              | Min            | Тур                                    | Max                         | Unit |

|----------------------------------------------------|---------------------|----------------|----------------------------------------|-----------------------------|------|

| Cycle time, SCLK                                   | t <sub>c</sub>      | 244            | 1/256 Fs                               |                             | ns   |

| SCLK Duty Cycle                                    | t <sub>dty</sub>    | _              | 50                                     |                             | %    |

| Delay Time, SCLK↑ to $\overline{FSYNC}$ ↓          | t <sub>d1</sub>     | _              | _                                      | 20                          | ns   |

| Delay Time, SCLK↑ to SDO Valid                     | t <sub>d2</sub>     | _              | _                                      | 20                          | ns   |

| Delay Time, SCLK↑ to <del>FSYNC</del> ↑            | t <sub>d3</sub>     | _              | _                                      | 20                          | ns   |

| Setup Time, SDI Before SCLK $\downarrow$           | t <sub>su</sub>     | 25             | _                                      |                             | ns   |

| Hold Time, SDI After SCLK $\downarrow$             | t <sub>h</sub>      | 20             | _                                      |                             | ns   |

| Setup Time, FC↑ Before SCLK↑                       | t <sub>sfc</sub>    | 40             | _                                      |                             | ns   |

| Hold time, FC↑ After SCLK↑                         | t <sub>hfc</sub>    | 40             | _                                      | _                           | ns   |

| Note: All timing is referenced to the 50% level of | the waveform. Input | test levels ar | e V <sub>IH</sub> = V <sub>D</sub> – 0 | .4 V, V <sub>IL</sub> = 0.4 | V.   |

Figure 3. Serial Interface Timing Diagram (DCE = 0)

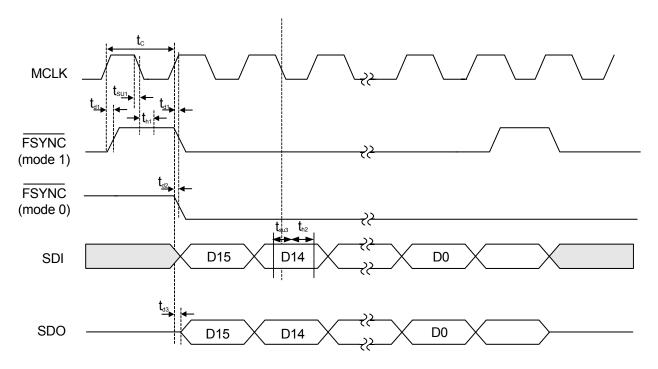

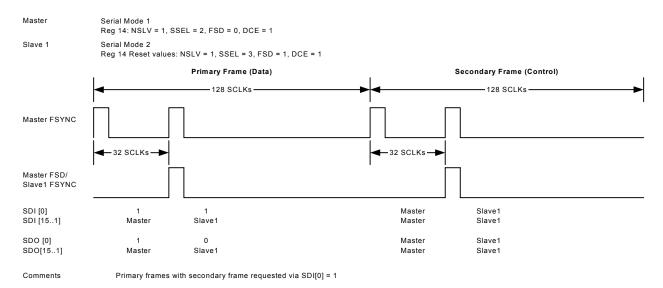

### Table 8. Switching Characteristics—Serial Interface (Master Mode, DCE = 1, FSD = 0)

$(V_A = Charge Pump, V_D = 3.0 \text{ to } 3.6 \text{ V}, T_A = 0 \text{ to } 70 \text{ °C}, C_L = 20 \text{ pF})$

| Symbol           | Min                                                                                                                                                                                         | Тур                                                    | Max                                                    | Unit                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| t <sub>c</sub>   | 244                                                                                                                                                                                         | 1/256 Fs                                               |                                                        | ns                                                     |

| t <sub>dty</sub> |                                                                                                                                                                                             | 50                                                     |                                                        | %                                                      |

| t <sub>d1</sub>  |                                                                                                                                                                                             | —                                                      | 20                                                     | ns                                                     |

| t <sub>d2</sub>  |                                                                                                                                                                                             | _                                                      | 20                                                     | ns                                                     |

| t <sub>d3</sub>  |                                                                                                                                                                                             | _                                                      | 20                                                     | ns                                                     |

| t <sub>d4</sub>  |                                                                                                                                                                                             | _                                                      | 20                                                     | ns                                                     |

| t <sub>d5</sub>  |                                                                                                                                                                                             | _                                                      | 20                                                     | ns                                                     |

| t <sub>d6</sub>  |                                                                                                                                                                                             | _                                                      | 20                                                     | ns                                                     |

| t <sub>su</sub>  | 25                                                                                                                                                                                          | —                                                      |                                                        | ns                                                     |

| t <sub>h</sub>   | 20                                                                                                                                                                                          | _                                                      |                                                        | ns                                                     |

|                  | $\begin{array}{c c} & t_{c} \\ \hline t_{dty} \\ \hline t_{d1} \\ \hline t_{d2} \\ \hline t_{d3} \\ \hline t_{d4} \\ \hline t_{d5} \\ \hline t_{d6} \\ \hline t_{su} \\ \hline \end{array}$ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |

#### Notes:

1. All timing is referenced to the 50% level of the waveform. Input test levels are  $V_{IH} = V_D - 0.4 V$ ,  $V_{IL} = 0.4 V$ .

2. See "5.27. Multiple Device Support" on page 38 for functional details.

12

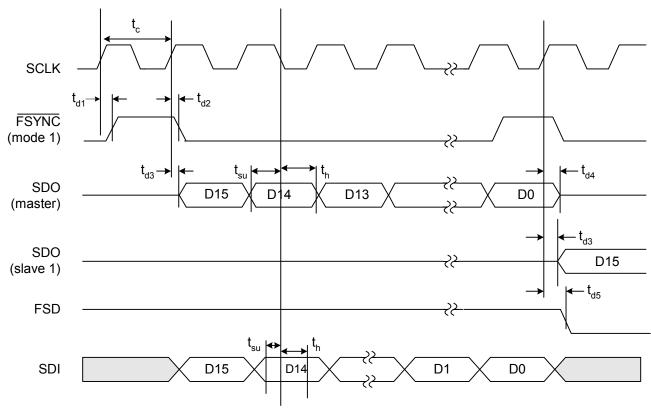

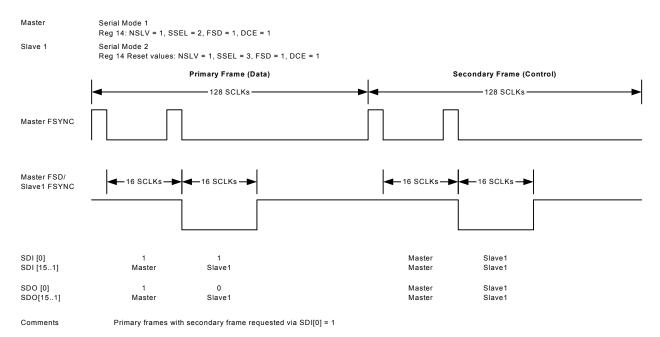

### Table 9. Switching Characteristics—Serial Interface (Master Mode, DCE = 1, FSD = 1)

| $(V_D = 3.0 \text{ to } 3.6 \text{ V}, T_A = 0 \text{ to } 70 \text{ °C}, C_L = 20 \text{ p}$ | pF) |

|-----------------------------------------------------------------------------------------------|-----|

|-----------------------------------------------------------------------------------------------|-----|

| Symbol           | Min                                                                                                              | Тур                                                    | Max                                                    | Unit                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| t <sub>c</sub>   | 244                                                                                                              | 1/256 Fs                                               |                                                        | ns                                                     |

| t <sub>dty</sub> | _                                                                                                                | 50                                                     |                                                        | %                                                      |

| t <sub>d1</sub>  | _                                                                                                                | _                                                      | 20                                                     | ns                                                     |

| t <sub>d2</sub>  |                                                                                                                  | _                                                      | 20                                                     | ns                                                     |

| t <sub>d3</sub>  | _                                                                                                                | _                                                      | 20                                                     | ns                                                     |

| t <sub>d4</sub>  | _                                                                                                                | _                                                      | 20                                                     | ns                                                     |

| t <sub>d5</sub>  |                                                                                                                  | _                                                      | 20                                                     | ns                                                     |

| t <sub>su</sub>  | 25                                                                                                               | _                                                      |                                                        | ns                                                     |

| t <sub>h</sub>   | 20                                                                                                               |                                                        |                                                        | ns                                                     |

|                  | $\begin{array}{c c} t_{c} \\ t_{dty} \\ t_{d1} \\ t_{d2} \\ t_{d3} \\ t_{d4} \\ t_{d5} \\ t_{su} \\ \end{array}$ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ |

#### Notes:

1. All timing is referenced to the 50% level of the waveform. Input test levels are  $V_{IH} = V_D - 0.4 \text{ V}$ ,  $V_{IL} = 0.4 \text{ V}$ . 2. See "5.27.Multiple Device Support" on page 38 for functional details.

Figure 5. Serial Interface Timing Diagram (DCE = 1, FSD = 1)

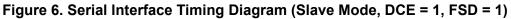

### Table 10. Switching Characteristics—Serial Interface (Slave Mode, DCE = 1, FSD = 1)

$(V_A = Charge Pump, V_D = 3.0 \text{ to } 3.6 \text{ V}, T_A = 0 \text{ to } 70 \text{ }^\circ\text{C}, C_L = 20 \text{ pF})$

| Parameter                                                              | Symbol           | Min                   | Тур           | Мах                 | Unit    |

|------------------------------------------------------------------------|------------------|-----------------------|---------------|---------------------|---------|

| Cycle Time, MCLK                                                       | t <sub>c</sub>   | 244                   | 1/256 Fs      |                     | ns      |

| Setup Time, FSYNC $\uparrow$ before MCLK $\downarrow^*$                | t <sub>su1</sub> | _                     |               | 20                  | ns      |

| Delay Time, FSYNC↑ after MCLK↓*                                        | t <sub>d1</sub>  | _                     |               | 20                  | ns      |

| Setup Time, SDI before MCLK $\downarrow$                               | t <sub>su3</sub> | _                     |               | 20                  | ns      |

| Hold Time, SDI After MCLK $\downarrow$                                 | t <sub>h2</sub>  | _                     |               | 20                  | ns      |

| Delay Time, MCLK↑ to SDO                                               | t <sub>d3</sub>  | _                     |               | 20                  | ns      |

| Delay Time, MCLK↑ to FSYNC↑                                            | t <sub>d1</sub>  | _                     |               | 20                  | ns      |

| Delay Time, MCLK $\uparrow$ to FSYNC $\downarrow$                      | t <sub>d2</sub>  | —                     |               | 20                  | ns      |

| *Note: T <sub>su1</sub> and T <sub>h1</sub> are listed for application | ns where the cor | ntroller drives the N | ICLK and FSYN | C instead of a mast | er DAA. |

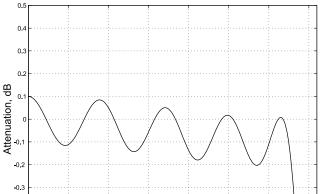

### Table 11. Digital FIR Filter Characteristics—Transmit and Receive

$(V_D = 3.0 \text{ to } 3.6 \text{ V}, \text{ Sample Rate} = 8 \text{ kHz}, T_A = 0 \text{ to } 70 \text{ °C})$

| Parameter                                    | Symbol                | Min             | Тур              | Max | Unit |

|----------------------------------------------|-----------------------|-----------------|------------------|-----|------|

| Passband (0.1 dB)                            | F <sub>(0.1 dB)</sub> | 0               | _                | 3.3 | kHz  |

| Passband (3 dB)                              | F <sub>(3 dB)</sub>   | 0               | _                | 3.6 | kHz  |

| Passband Ripple Peak-to-Peak                 |                       | -0.1            |                  | 0.1 | dB   |

| Stopband                                     |                       | _               | 4.4              |     | kHz  |

| Stopband Attenuation                         |                       | -74             | _                |     | dB   |

| Group Delay                                  | t <sub>gd</sub>       |                 | 12/Fs            |     | S    |

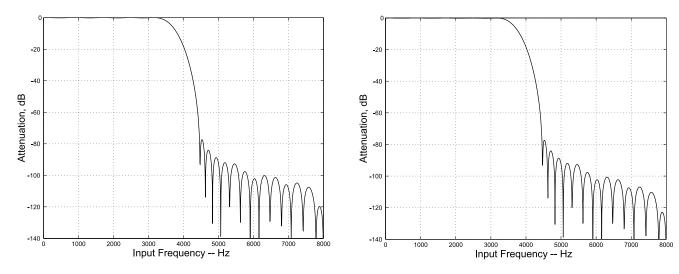

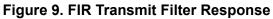

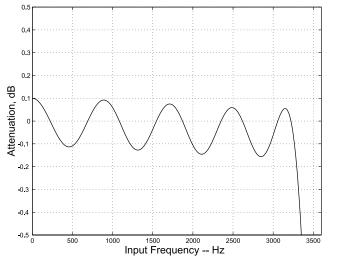

| Note: Typical FIR filter characteristics for | Fs = 8000 Hz are s    | hown in Figures | 7, 8, 9, and 10. | 1   | 1    |

### Table 12. Digital IIR Filter Characteristics—Transmit and Receive

| Parameter                                                                          | Symbol              | Min             | Тур              | Max             | Unit          |

|------------------------------------------------------------------------------------|---------------------|-----------------|------------------|-----------------|---------------|

| Passband (3 dB)                                                                    | F <sub>(3 dB)</sub> | 0               | _                | 3.6             | kHz           |

| Passband Ripple Peak-to-Peak                                                       |                     | -0.2            | _                | 0.2             | dB            |

| Stopband                                                                           |                     |                 | 4.4              |                 | kHz           |

| Stopband Attenuation                                                               |                     | -40             |                  |                 | dB            |

| Group Delay                                                                        | t <sub>gd</sub>     | _               | 1.6/Fs           |                 | S             |

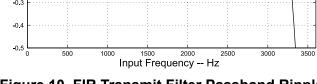

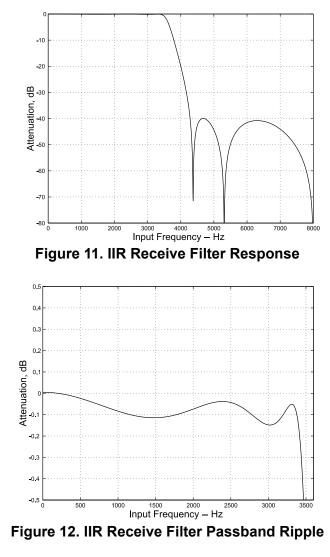

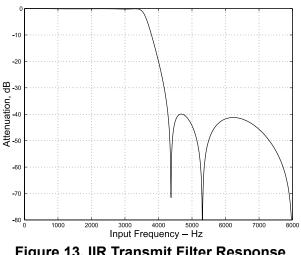

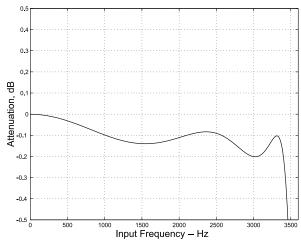

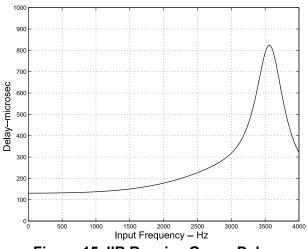

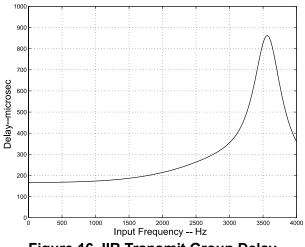

| Note: Typical IIR filter characteristics for F group delay versus input frequency. | s = 8000 Hz are     | shown in Figure | s 11, 12, 13, an | d 14. Figures 1 | 5 and 16 show |

$(V_D = 3.0 \text{ to } 3.6 \text{ V}, \text{ Sample Rate} = 8 \text{ kHz}, T_A = 0 \text{ to } 70 \text{ °C})$

Figure 7. FIR Receive Filter Response

Figure 8. FIR Receive Filter Passband Ripple

Figure 10. FIR Transmit Filter Passband Ripple

For Figures 7–10, all filter plots apply to a sample rate of Fs = 8 kHz.

Figure 13. IIR Transmit Filter Response

Figure 14. IIR Transmit Filter Passband Ripple

Figure 15. IIR Receive Group Delay

Figure 16. IIR Transmit Group Delay

# Si3056 <u>Si3018/19/10</u>

### 2. Typical Application Schematic

### 3. Bill of Materials

| Component(s)          | Value                                  | Supplier(s)               |

|-----------------------|----------------------------------------|---------------------------|

| C1, C2                | 33 pF, Y2, X7R, ±20%                   | Panasonic, Murata, Vishay |

| C3 <sup>1</sup>       | 10 nF, 250 V, X7R, ±10%                | Venkel, SMEC              |

| C4                    | 1.0 uF, 50 V, Elec/Tant, ±20%          | Panasonic                 |

| C5, C6, C50, C51      | 0.1 uF, 16V, X7R, ±20%                 | Venkel, SMEC              |

| C7                    | 2.7 nF, 50V, X7R, 20%                  | Venkel, SMEC              |

| C8, C9                | 680 pF, Y2, X7R, ±10%                  | Panasonic, Murata, Vishay |

| C10                   | 0.01 uF, 16 V, X7R, ±20%               | Venkel, SMEC              |

| C30, C31 <sup>3</sup> | Not installed, 120 pF, 250V, X7R, ±10% | Venkel, SMEC              |

| D1, D2 <sup>2</sup>   | Dual Diode, 225 mA, 300 V, CMPD2004S   | Central Semiconductor     |

| FB1, FB2              | Ferrite Bead, BLM18AG601SN1B           | Murata                    |

| Q1, Q3                | NPN, 300 V, MMBTA42                    | OnSemi, Fairchild         |

| Q2                    | PNP, 300 V, MMBTA92                    | OnSemi, Fairchild         |

| Q4, Q5                | NPN, 80 V, 330 mW, MMBT2484            | OnSemi, Fairchild         |

| RV1                   | Sidactor, 275 V, 100 A                 | Teccor, Protek, ST Micro  |

| R1                    | 1.07 kohm, 1/2 W, 1%                   | Venkel, SMEC, Panasonic   |

| R2                    | 150 ohm, 1/16 W, 5%                    | Venkel, SMEC, Panasonic   |

| R3                    | 3.65 kohm, 1/2 W, 1%                   | Venkel, SMEC, Panasonic   |

| R4                    | 2.49 kohm, 1/2 W, 1%                   | Venkel, SMEC, Panasonic   |

| R5, R6                | 100 kohm, 1/16 W, 5%                   | Venkel, SMEC, Panasonic   |

| R7, R8 <sup>3</sup>   | 20 Mohm, 1/16 W, 5%                    | Venkel, SMEC, Panasonic   |

| R9                    | 1 Mohm, 1/16 W, 1%                     | Venkel, SMEC, Panasonic   |

| R10                   | 536 ohm, 1/4 W, 1%                     | Venkel, SMEC, Panasonic   |

| R11                   | 73.2 ohm, 1/2 W, 1%                    | Venkel, SMEC, Panasonic   |

| R12, R13              | 56.2 ohm, 1/16 W, 1%                   | Venkel, SMEC, Panasonic   |

| R15, R16 <sup>4</sup> | 0 ohm, 1/16 W                          | Venkel, SMEC, Panasonic   |

| R30, R32 <sup>3</sup> | Not installed, 15 Mohm,, 1/8 W, 5%     | Venkel, SMEC, Panasonic   |

| R31, R33 <sup>3</sup> | Not installed, 5.1 Mohm,, 1/8 W, 5%    | Venkel, SMEC, Panasonic   |

| R51, R52              | 4.7 kohm,, 1/10 W, 5%                  | Venkel, SMEC, Panasonic   |

| U1                    | Si3056                                 | Silicon Labs              |

| U2                    | Si3018/19/10                           | Silicon Labs              |

| Z1                    | Zener Diode, 43 V, 1/2 W, ZMM43        | General Semiconductor     |

1. Value for C3 above is recommended for use with the Si3018. In voice appliations, a C3 value of 3.9 nF (250 V, X7R, 20%) is recommended to improve return loss performance

2. Several diode bridge configurations are acceptable, parts such as a single DF-04S or four 1N4004 diodes may be used (suppliers include General Semiconductor, Diodes Inc., etc.)

3. C30-31 and R30-33 can be substitued for R7-8 to implent the enhanced caller ID circuit.

4. Murata BLM18AG601SN1B may be substituted for R15-R16 (0 ohm) to decrease emissions.

### 4. AOUT PWM Output

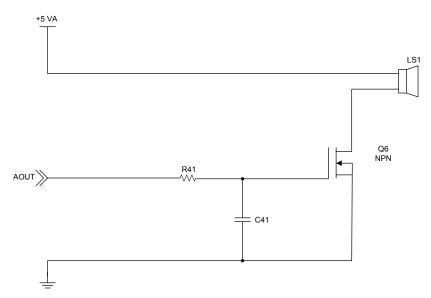

Figure 18 illustrates an optional circuit to support the pulse width modulation (PWM) output capability of the Si3056 for call progress monitoring purposes. Set the PWME bit (Register 1, bit 3) to enable this mode.

Figure 18. AOUT PWM Circuit for Call Progress

| Component | ponent Value Supplier   |                         |  |  |

|-----------|-------------------------|-------------------------|--|--|

| LS1       | Speaker BRT1209PF-06    | Intervox                |  |  |

| Q6        | NPN KSP13               | Fairchild               |  |  |

| C41       | 0.1 μF, 16 V, X7R, ±20% | Venkel, SMEC            |  |  |

| R41       | 150 Ω, 1/16 W, ±5%      | Venkel, SMEC, Panasonic |  |  |

Registers 20 and 21 allow the receive and transmit paths to be attenuated linearly. When these registers are set to all 0s, the receive and transmit paths are muted. These registers affect the call progress output only and do not affect transmit and receive operations on the telephone line.

The PWMM[1:0] bits (Register 1, bits 5:4) select one of the three different PWM output modes for the AOUT signal, including a delta-sigma data stream, a conventional 32 kHz return to zero PWM output, and balanced 32 kHz PWM output.

20

### 5. Functional Description

The Si3056 is an integrated direct access arrangement (DAA) that provides a programmable line interface to meet global telephone line interface requirements. The Si3056 implements Silicon Laboratories<sup>®</sup> patented isolation technology and offers the highest level of integration by replacing an analog front end (AFE), an isolation transformer, relays, opto-isolators, and a 2- to 4-wire hybrid with two 16-pin packages.

The Si3056 DAA is software programmable to meet global requirements and is compliant with FCC, TBR21, JATE, and other country-specific PTT specifications as shown in Table 16 on page 26. In addition, the Si3056 meets the most stringent worldwide requirements for out-of-band energy, emissions, immunity, high-voltage surges, and safety, including FCC Part 15 and 68, EN55022, EN55024, and many other standards.

# 5.1. Upgrading from the Si3034/35/44 to Si3056

The Si3056 offers Silicon Laboratories<sup>®</sup> customers currently using Si3034/35/44 standard serial interface DAA chipsets with an upgrade path for use in new designs. The Si3056 digital interface is similar to the Si3034/35/44 DAAs, thus the Si3056 retains the ability to connect to many widely available DSPs. This also allows customers to leverage software developed for existing Si3034/35/44 designs. More importantly, the Si3056 also offers a number of new features not provided in the Si3034/35/44 DAAs. An overview of the feature differences between the Si3044 and the Si3056 is presented in Table 14. Finally, the globally-compliant Si3056 can be implemented with roughly half the external components required in the already highly integrated Si3034/35/44 DAA application circuits. The following items have changed in the Si3056 as compared to the Si3034/35/44 DAAs:

The pinout, the application circuit, and the bill of materials. The Si3056 is not pin compatible with Si3034/35/44 DAA chipsets.

- New features have been added to the Si3056 including more ac terminations, a programmable hybrid, finer gain/attenuation step resolution, finer resolution loop current monitoring capability, ring validation, more HW interrupts, a 200 Hz low frequency filter pole. (See the appropriate functional descriptions.)

- The secondary communication data format (see "5.26.Digital Interface" on page 37).

- The low-power sleep mode, and system requirements to support wake-on-ring. (See "5.28.Power Management" on page 39.)

### 5.2. Line-Side Device Support

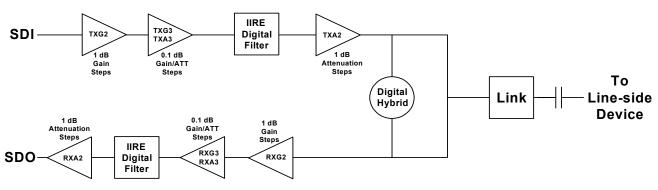

Three different line-side devices can be used with the Si3056 system-side device:

- Globally-compliant line-side device—Targets global DAA requirements. Use the Si3018 global line-side device for this configuration. This line-side device supports both FCC-compliant countries and non-FCC-compliant countries.

- Globally-compliant, enhanced features line-side device—Targets embedded and voice applications with global DAA requirements. Use the Si3019 lineside device for this configuration. The Si3019 contains all the features available on the Si3018, plus the following additional features/enhancements:

- Sixteen selectable ac terminations to increase return loss and trans-hybrid loss performance.

- Higher transmit and receive level mode.

- Selectable 200 Hz low frequency pole.

- -16 to 13.5 dB digital gain/attenuation adjustment in 0.1 dB increments for the transmit and receive paths.

- Programmable line current/voltage threshold interrupt.

- Globally-compliant, low-speed only line-side device—Targets embedded 2400 bps soft modem applications. Use the Si3010 line-side device for this configuration. The Si3010 contains all the features available on the Si3018, except the transmit and receive paths are optimized and tested only for modem connect rates up to 2400 bps.

# Si3056 <u>Si3018/19/10</u>

### Table 14. New Si3056 Features

| Chipset                              | Si3044           |                    | Si3056             |                    |  |  |  |

|--------------------------------------|------------------|--------------------|--------------------|--------------------|--|--|--|

| System-Side Part #                   | Si3021           | -                  | S13056             |                    |  |  |  |

| Line-Side Part #                     | Si3015           | Si3010             | Si3018             | Si3019             |  |  |  |

| Global DAA                           | Yes              | Yes                | Yes                | Yes                |  |  |  |

| Digital Interface                    | SSI              | SSI                | SSI                | SSI                |  |  |  |

| Power Supply                         | 3.3 V or 5 V     | 3.3 V              | 3.3 V              | 3.3 V              |  |  |  |

| Max Modem Connect Rate               | 56 kbps          | 2400 bps           | 56 kbps            | 56 kbps            |  |  |  |

| Data Bus Width                       | 16-bit           | 16-bit             | 16-bit             | 16-bit             |  |  |  |

| Control Register Addressing          | 6-bit            | 8-bit              | 8-bit              | 8-bit              |  |  |  |

| Max Sampling Frequency               | 11.025 kHz       | 16 kHz             | 16 kHz             | 16 kHz             |  |  |  |

| AC Terminations                      | 2                | 4                  | 4                  | 16                 |  |  |  |

| Programmable Gain                    | 3 dB steps       | 3 dB steps         | 3 dB steps         | 0.1 dB steps       |  |  |  |

| Loop Current Monitoring              | 3 mA/bit         | 1.1 mA/bit         | 1.1 mA/bit         | 1.1 mA/bit         |  |  |  |

| Line Voltage Monitoring              | 2.75 V per bit   | 1 V per bit        | 1 V per bit        | 1 V per bit        |  |  |  |

| Polarity Reversal Detection          | Yes (SW polling) | Yes (HW interrupt) | Yes (HW interrupt) | Yes (HW interrupt) |  |  |  |

| Line I/V Threshold Detection         | No               | No                 | No                 | Yes                |  |  |  |

| Ring Qualification                   | No               | Yes                | Yes                | Yes                |  |  |  |

| Wake-on-Ring Support                 | Yes              | Yes (MCLK active)  | Yes (MCLK active)  | Yes (MCLK active)  |  |  |  |

| HW Interrupts                        | Ring detect only | 7 HW interrupts    | 7 HW interrupts    | 8 HW interrupts    |  |  |  |

| Integrated Fixed Analog<br>Hybrid    | Yes              | Yes                | Yes                | Yes                |  |  |  |

| Programmable Digital Hybrid          | No               | Yes                | Yes                | Yes                |  |  |  |

| Full Scale Transmit/Receive<br>Level | +3.2 dBm         | 0 dBm              | 0 dBm              | +3.2 dBm           |  |  |  |

22

| Register               | 16  | 31   | 16 | 16 | 26   | 26       | 26        | 30 <sup>2</sup> | 1   | 6 <sup>3</sup> |

|------------------------|-----|------|----|----|------|----------|-----------|-----------------|-----|----------------|

| Country                | OHS | OHS2 | RZ | RT | ILIM | DCV[1:0] | MINI[1:0] | ACIM[3:0]       | ACT | ACT2           |

| Argentina              | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Australia <sup>4</sup> | 1   | 0    | 0  | 0  | 0    | 01       | 01        | 0011            | 0   | 1              |

| Austria                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Bahrain                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Belgium                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Brazil                 | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Bulgaria               | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0011            | 0   | 1              |

| Canada                 | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Chile                  | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| China <sup>5</sup>     | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000/1010       | 0   | 0              |

| Colombia               | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Croatia                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Cyprus                 | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Czech Republic         | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Denmark                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Ecuador                | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Egypt                  | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| El Salvador            | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Finland                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| France                 | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Germany                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Greece                 | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Guam                   | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Hong Kong              | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Hungary                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Iceland                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| India                  | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Indonesia              | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Ireland                | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Israel                 | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Italy                  | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Japan                  | 0   | 0    | 0  | 0  | 0    | 01       | 01        | 0000            | 0   | 0              |

| Jordan                 | 0   | 0    | 0  | 0  | 0    | 01       | 01        | 0000            | 0   | 0              |

| Kazakhstan             | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Kuwait                 | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Latvia                 | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

### **Table 15. Country Specific Register Settings**

Note:

**1.** Supported for loop current  $\ge$  20 mA.

2. Available with Si3019 line-side only.

3. Available with Si3018 and Si3010 line-sides only.

4. See "5.11.DC Termination" on page 27 for DCV and MINI settings.

5. ACIM is 0000 for data applications and 1010 for voice applications.

6. For South Korea, set the TB3 bit in conjunction with the RZ bit. (See Register 59 description.)

Downloaded from Elcodis.com electronic components distributor

Rev. 1.05

## Si3056 <u>Si3018/19/10</u>

| Register                 | 16  | 31   | 16 | 16 | 26   | 26       | 26        | 30 <sup>2</sup> | 1   | 6 <sup>3</sup> |

|--------------------------|-----|------|----|----|------|----------|-----------|-----------------|-----|----------------|

| Country                  | OHS | OHS2 | RZ | RT | ILIM | DCV[1:0] | MINI[1:0] | ACIM[3:0]       | ACT | ACT2           |

| Lebanon                  | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Luxembourg               | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Масао                    | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Malaysia <sup>1</sup>    | 0   | 0    | 0  | 0  | 0    | 01       | 01        | 0000            | 0   | 0              |

| Malta                    | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Mexico                   | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Morocco                  | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Netherlands              | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| New Zealand              | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0100            | 1   | 1              |

| Nigeria                  | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Norway                   | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Oman                     | 0   | 0    | 0  | 0  | 0    | 01       | 01        | 0000            | 0   | 0              |

| Pakistan                 | 0   | 0    | 0  | 0  | 0    | 01       | 01        | 0000            | 0   | 0              |

| Peru                     | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Philippines              | 0   | 0    | 0  | 0  | 0    | 01       | 01        | 0000            | 0   | 0              |

| Poland                   | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Portugal                 | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Romania                  | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Russia                   | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Saudi Arabia             | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Singapore                | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Slovakia                 | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Slovenia                 | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| South Africa             | 0   | 0    | 1  | 0  | 0    | 11       | 00        | 0011            | 1   | 0              |

| South Korea <sup>6</sup> | 0   | 0    | 1  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Spain                    | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Sweden                   | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Switzerland              | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Taiwan                   | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| TBR21                    | 0   | 0    | 0  | 0  | 1    | 11       | 00        | 0010            | 0   | 1              |

| Thailand                 | 0   | 0    | 0  | 0  | 0    | 01       | 01        | 0000            | 0   | 0              |

| UAE                      | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| United Kingdom           | 0   | 1    | 0  | 0  | 1    | 11       | 00        | 0101            | 0   | 1              |

| USA                      | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

| Yemen                    | 0   | 0    | 0  | 0  | 0    | 11       | 00        | 0000            | 0   | 0              |

Table 15. Country Specific Register Settings (Continued)

Note:

**1.** Supported for loop current  $\ge$  20 mA.

2. Available with Si3019 line-side only.

**3.** Available with Si3018 and Si3010 line-sides only.

4. See "5.11.DC Termination" on page 27 for DCV and MINI settings.

5. ACIM is 0000 for data applications and 1010 for voice applications.

6. For South Korea, set the TB3 bit in conjunction with the RZ bit. (See Register 59 description.)

### 5.3. Power Supplies

The Si3056 system-side device operates from a 3.0– 3.6 V power supply. The Si3056 input pins are 5 V tolerant. The Si3056 output pins only drive 3.3 V. The line-side device derives its power from two sources: The Si3056 and the telephone line. The Si3056 supplies power over the patented isolation link between the two devices, allowing the line-side device to communicate with the Si3056 while on-hook and perform other onhook functions such as line voltage monitoring. When off-hook, the line-side device also derives power from the line current supplied from the telephone line. This feature is exclusive to DAAs from Silicon Laboratories<sup>®</sup> and allows the most cost-effective implementation for a DAA while still maintaining robust performance over all line conditions.

### 5.4. Initialization

When the Si3056 is powered up, assert the RESET pin. When the RESET pin is deasserted, the registers have default values. This reset condition guarantees the lineside device is powered down without the possibility of loading the line (i.e., off-hook). An example initialization procedure is outlined in the following list:

- Program the PLL with registers 8 and 9 (N[7:0], M[7:0]) to the appropriate divider ratios for the supplied MCLK frequency and the sample rate in register 7 (SRC), as defined in "5.25.Clock Generation" on page 36.

- 2. Wait 1 ms until the PLL is locked.

- 3. Write a 00H into Register 6 to power up the line-side device.

- Set the required line interface parameters (i.e., DCV[1:0], MINI[1:0], ILIM, DCR, ACT and ACT2 or ACIM[3:0], OHS, RT, RZ, ATX[2:0] or TGA2 and TXG2) as defined by "Country Specific Register Settings" shown in Table 15.

When this procedure is complete, the Si3056 is ready for ring detection and off-hook.

### 5.5. Isolation Barrier

The Si3056 achieves an isolation barrier through lowcost, high-voltage capacitors in conjunction with Silicon Laboratories<sup>®</sup> proprietary signal processing techniques. These techniques eliminate signal degradation from capacitor mismatches, common mode interference, or noise coupling. As shown in Figure 17 on page 18, the C1, C2, C8, and C9 capacitors isolate the Si3056 (system-side) from the line-side device. Transmit, receive, control, ring detect, and caller ID data are passed across this barrier. Y2 class capacitors can be used to achieve surge performance of 5 kV or greater.

The capacitive communications link is disabled by default. To enable it, the PDL bit (Register 6, bit 4) must be cleared. No communication between the systemside and line-side can occur until this bit is cleared. The clock generator must be programmed to an acceptable sample rate before clearing the PDL bit.

# 5.6. Transmit/Receive Full Scale Level (Si3019 Line-Side Only)

The Si3056 supports programmable maximum transmit and receive levels. The default signal level supported by the Si3056 is 0 dBm into a 600  $\Omega$  load. Two additional modes of operation offer increased transmit and receive level capability to enable use of the DAA in applications that require higher signal levels. The full scale mode is enabled by setting the FULL bit in Register 31. With FULL = 1, the full scale signal level increases to +3.2 dBm into a 600  $\Omega$  load, or 1 dBV into all reference impedances. The enhanced full scale mode (or 2X full scale) is enabled by setting the FULL2 bit in Register 30. Will FULL2 = 1, the full scale signal level increases to +6.0 dBm into a 600  $\Omega$  load, or 1.5 dBV into all reference impedances. The full scale and enhanced full scale modes provide the ability to trade off TX power and TX distortion for a peak signal. By using the programmable digital gain registers in conjunction with the enhanced full scale signal level mode, a specific power level (+3.2 dBm for example) could be achieved across all ACT settings.

### 5.7. Parallel Handset Detection

The Si3056 can detect a parallel handset going offhook. When the Si3056 is off-hook, the loop current can be monitored with the LCS bits. A significant drop in loop current signals that a parallel handset is going offhook. If a parallel handset causes the LCS bits to read all 0s, the Drop-Out Detect (DOD) bit can be checked to verify a valid line exists.

The LVS bits can be read to determine the line voltage when on-hook and off-hook. Significant drops in line voltage can signal a parallel handset. For the Si3056 to operate in parallel with another handset, the parallel handset must have a sufficiently high dc termination to support two off-hook DAAs on the same line. Improved parallel handset operation can be achieved by changing the dc impedance from 50 to 800  $\Omega$  and reducing the DCT pin voltage with the DVC[1:0] bits.

### 5.8. Line Voltage/Loop Current Sensing

The Si3056 can measure loop current and line voltage with the Si3010, Si3018, and the Si3019 line-side devices. The 8-bit LCS2[7:0] and LCS[4:0] registers report loop current. The 8-bit LVS[7:0] register reports line voltage.

Downloaded from Elcodis.com electronic components distributor

These registers can help determine the following:

- When on-hook, detect if a line is connected.

- When on-hook, detect if a parallel phone is off-hook.

- When off-hook, detect if a parallel phone goes on or off-hook.

- Detect if enough loop current is available to operate.

- When used in conjunction with the OPD bit, detect if an overcurrent condition exists. (See "5.22.Overload Detection" on page 35.)

#### 5.8.1. Line Voltage Measurement

The Si3056 device reports line voltage with the LVS[7:0] bits (Register 29) in both on- and off-hook states with a resolution of 1 V per bit. The accuracy of these bits is approximately  $\pm 10\%$ . Bits 0 through 6 of this register indicate the value of the line voltage in 2s compliment format. Bit 7 of this register indicates the polarity of the tip/ring voltage.

If the INTE bit (Register 2) and the POLM bit (Register 3) are set, a hardware interrupt is generated on the AOUT/INT pin when bit 7 of the LVS register changes state. The edge-triggered interrupt is cleared by writing 0 to the POLI bit (Register 4). The POLI bit is set each time bit 7 of the LVS register changes state and must be written to 0 to clear it.

The default state of the LVS register forces the LVS bits to 0 when the line voltage is 3 V or less. The LVFD bit (Register 31, bit 0) disables the force-to-zero function and allows the LVS register to display non-zero values of 3 V and below. This register might display unpredictable values at line voltages between 0 to 2 V. At 0 V, the LVS register displays all 0s.

#### 5.8.2. Loop Current Measurement

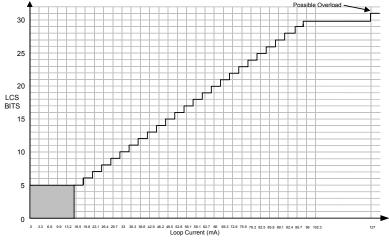

When the Si3056 is off-hook, the LCS2[7:0] and LCS[4:0] bits measure loop current in 1.1 mA/bit and 3.3 mA/bit resolution respectively. These bits enable

detection of another phone going off-hook by monitoring the dc loop current. The LCS bits are decoded from LCS2; so, both are available at the same time. The line current sense transfer function is shown in Figure 19 and detailed in Table 16. The LCS and LCS2 bits report loop current down to the minimum operating loop current for the DAA. Below this threshold, the reported value of loop current is unpredictable.

| LCS[4:0] | Condition                                                                                                                 |  |

|----------|---------------------------------------------------------------------------------------------------------------------------|--|

| 00000    | Insufficient line current for normal operation. Use the DOD bit (Register 19, bit 1) to determine if a line is connected. |  |

| 00100    | Minimum line current for normal operation.                                                                                |  |

| 11111    | Loop current is greater than 127 mA. An overcurrent situation may exist.                                                  |  |

### 5.9. Off-Hook

The communication system generates an off-hook command by applying a logic 0 to the OFHK pin or by setting the OH bit (Register 5, bit 0). The OFHK pin must be enabled by setting the OHE bit (Register 5, bit 1). The polarity of the OFHK pin is selected by the OPOL bit (Register 5, bit 4). With OFHK asserted, the system is in an off-hook state.

The off-hook state seizes the line for incoming/outgoing calls and also can be used for pulse dialing. With OFHK deasserted, negligible dc current flows through the hookswitch. When the OFHK pin is asserted, the hookswitch transistor pair, Q1 and Q2, turn on. This applies a termination impedance across TIP and RING and causes dc loop current to flow. The termination impedance has an ac and dc component.

Figure 19. Typical Loop Current LCS Transfer Function

Several events occur in the DAA when the  $\overline{OFHK}$  pin is asserted or the OH bit is set. There is a 250 µs latency to allow the off-hook command to be communicated to the line-side device. Once the line-side device goes offhook, an off-hook counter forces a delay for line transients to settle before transmission or reception occurs. This off-hook counter time is controlled by the FOH[1:0] bits (Register 31, bits 6:5). The default setting for the off-hook counter time is 128 ms, but can be adjusted up to 512 ms or down to either 64 or 8 ms.

After the off-hook counter has expired, a resistor calibration is performed for 17 ms. This allows circuitry internal to the DAA to adjust to the exact conditions present at the time of going off-hook. This resistor calibration can be disabled by setting the RCALD bit (Register 25, bit 5).

After the resistor calibration is performed, an ADC calibration is performed for 256 ms. This calibration helps to remove offset in the A/D sampling the telephone line. This ADC calibration can be disabled by setting the CALD bit (Register 17, bit 5). See "5.29.Calibration" on page 39. for more information on automatic and manual calibration.

Silicon Laboratories<sup>®</sup> recommends that the resistor and the ADC calibrations not be disabled except when a fast response is needed after going off-hook, such as when responding to a Type II caller-ID signal. See "5.21.Caller ID" on page 32.

To calculate the total time required to go off-hook and start transmission or reception, the digital filter delay (typically 1.5 ms with the FIR filter) should be included in the calculation.

### 5.10. Interrupts

The AOUT/INT pin can be used as a hardware interrupt pin by setting the INTE bit (Register 2, bit 7). When this bit is set, the call progress output function (AOUT) is not available. The default state of this interrupt output pin is active low, but active high operation can be enabled by setting the INTP bit (Register 2, bit 6). This pin is an open-drain output when the INTE bit is set, and requires a 4.7 kΩ pullup or pulldown for correct operation. If multiple INT pins are connected to a single input, the combined pullup or pulldown resistance should equal 4.7 kΩ. Bits 7-2, and 0 in Register 3 and bit 1 in Register 44 can be set to enable hardware interrupt sources. When one or more of these bits are set, the AOUT/INT pin becomes active and stays active until the interrupts are serviced. If more than one hardware interrupt is enabled in Register 3, software polling determines the cause of the interrupts. Register 4 and bit 3 of Register 44 contain sticky interrupt flag bits. Clear these bits after being set to service the interrupt.

Registers 43 and 44 contain the line current/voltage threshold interrupt. This interrupt will trigger when either the measured line voltage or current in the LVS or LCS2 registers, as selected by the CVS bit (Register 44, bit 2), crosses the threshold programmed into the CVT[7:0] bits. An interrupt can be programmed to occur when the measured value rises above or falls below the threshold. Only the magnitude of the measured value is used to compare to the threshold programmed into the CVT[7:0] bits, and thus only positive numbers should be used as a threshold. This line current/voltage threshold interrupt is only available with the Si3019 line-side device.

### 5.11. DC Termination

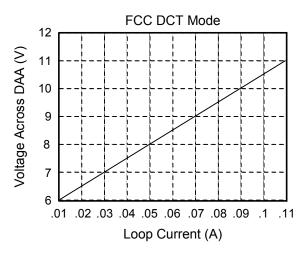

The DAA has programmable settings for dc impedance, minimum operational loop current, and TIP/RING voltage. The dc impedance of the DAA is normally represented with a 50  $\Omega$  slope as shown in Figure 20, but can be changed to an 800  $\Omega$  slope by setting the DCR bit. This higher dc termination presents a higher resistance to the line as loop current increases.

### Figure 20. FCC Mode I/V Characteristics, DCV[1:0] = 11, MINI[1:0] = 00, ILIM = 0

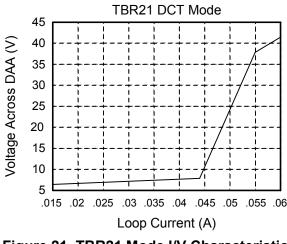

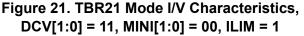

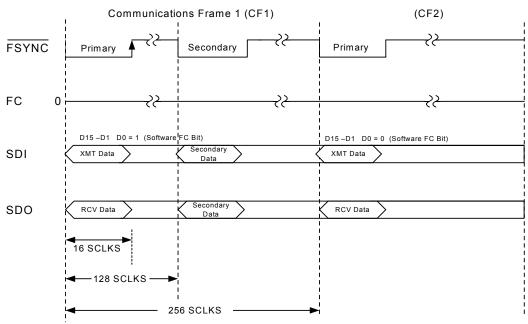

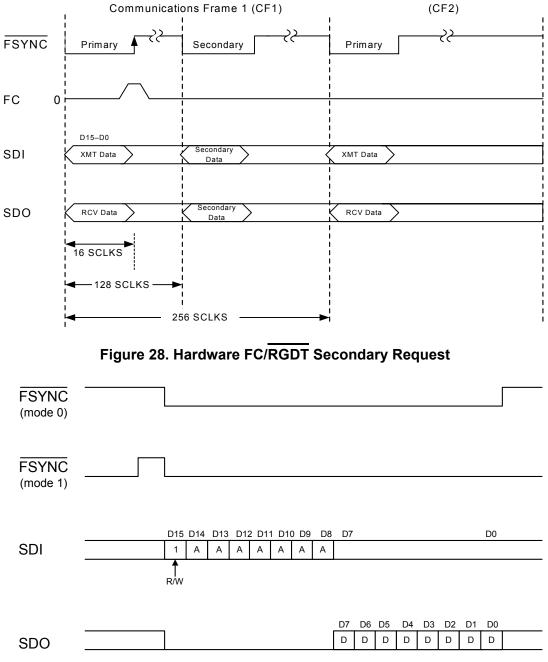

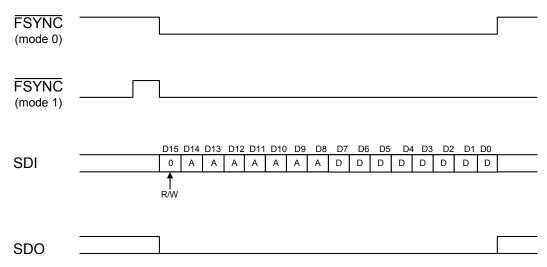

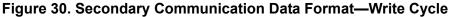

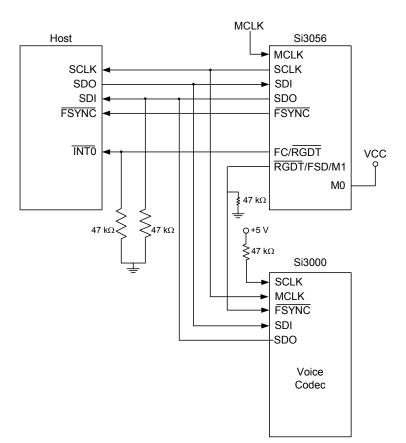

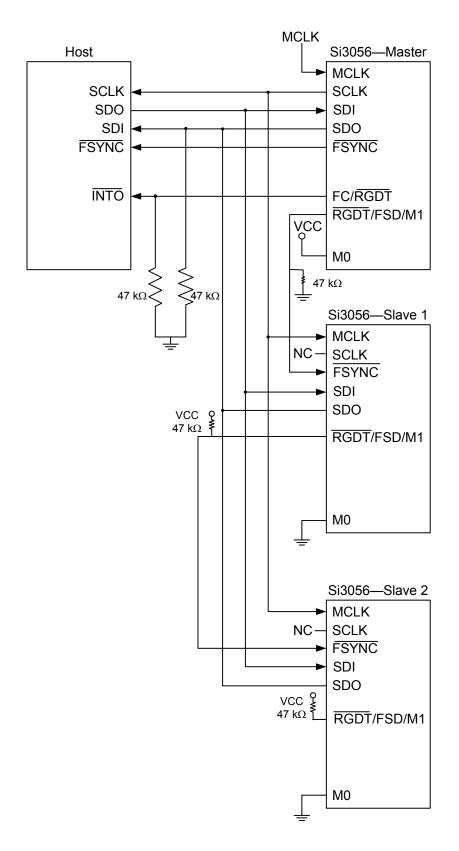

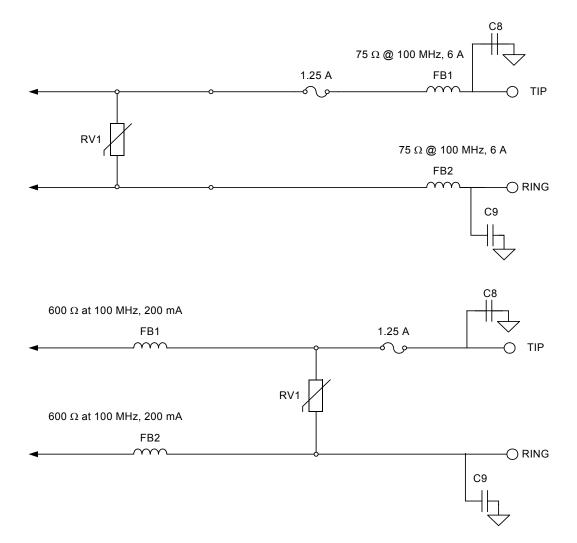

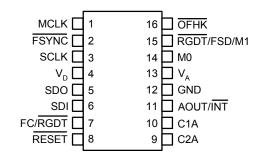

For applications that require current limiting per the TBR21 standard, the ILIM bit can be set to select this mode. In the current limiting mode, the dc I/V curve is changed to a 2000  $\Omega$  slope above 40 mA, as shown in Figure 21. The DAA operates with a 50 V, 230  $\Omega$  feed, which is the maximum line feed specified in the TBR21 standard.