## Half-Bridge MOSFET Driver for Switching Power Supplies

## **FEATURES**

- 4.5- to 5.5-V Operation

- Undervoltage Lockout

- 250-kHz to 1-MHz Switching Frequency

- Synchronous Switch Enable

- One Input PWM Signal Generates Both Drive

- Bootstrapped High-Side Drive

- Operates from 4.5- to 30-V Supply

- TTL/CMOS Compatible Input Levels

- 1-A Peak Drive Current

- Break-Before-Make Circuit

## **APPLICATIONS**

- Multiphase Desktop CPU Supplies

- Single-Supply Synchronous Buck Converters

- Mobile Computing CPU Core Power Converters

- Standard-Synchronous Converters

- High Frequency Switching Converters

## **DESCRIPTION**

The Si9913 is a dual MOSFET high-speed driver with break-before-make. It is designed to operate in high frequency dc-dc switchmode power supplies. The high-side driver is bootstrapped to handle the high voltage slew rate associated with "floating" high-side gate drivers. Each driver is capable of switching a 3000-pF load with 60-ns propogation delay and 25-ns transition time. The Si9913 comes with internal break-before-make feature to prevent shoot-through current in the external MOSFETs. A synschronous enable pin is used to

enable the low-side driver. When disabled, the  $\mbox{OUT}_L$  is logic low

The Si9913 is available in both standard and lead (Pb)-free 8-pin SOIC packages for operation over the industrial operation range  $(-40^{\circ}\text{C to }85^{\circ}\text{C})$ .

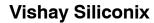

## **FUNCTIONAL BLOCK DIAGRAM AND TRUTH TABLE**

| TRUTH TABLE |     |    |                   |                   |  |  |

|-------------|-----|----|-------------------|-------------------|--|--|

| ٧s          | SYN | IN | V <sub>OUTL</sub> | V <sub>OUTH</sub> |  |  |

| L           | L   | L  | L                 | L                 |  |  |

| L           | L   | Н  | L                 | Н                 |  |  |

| L           | Н   | L  | Н                 | L                 |  |  |

| L           | Н   | Н  | L                 | Н                 |  |  |

| Н           | L   | L  | L                 | L                 |  |  |

| Н           | L   | Н  | L                 | Н                 |  |  |

| Н           | Н   | L  | L                 | L                 |  |  |

| Н           | Н   | Н  | L                 | Н                 |  |  |

| ABSOLUTE MAXIMUM RATINGS (T <sub>A</sub> = 25°C UNLESS OTHERWISE NOTED) |                                    |                                                 |      |  |

|-------------------------------------------------------------------------|------------------------------------|-------------------------------------------------|------|--|

| Parameter                                                               | Symbol                             | Limit                                           | Unit |  |

| Low Side Driver Supply Voltage                                          | $V_{DD}$                           | 7.0                                             |      |  |

| Input Voltage on IN                                                     | V <sub>IN</sub>                    | -0.3 to V <sub>DD</sub> +0.3                    |      |  |

| Synchronous Pin Voltage                                                 | V <sub>SYN</sub>                   | V <sub>SYN</sub> -0.3 to V <sub>DD</sub> +0.3 V |      |  |

| Bootstrap Voltage                                                       | V <sub>BOOT</sub>                  | 35.0                                            | 1    |  |

| High Side Driver (Bootstrap) Supply Voltage                             | V <sub>BOOT</sub> - V <sub>S</sub> | 7.0                                             |      |  |

| Operating Junction Temperature Range                                    | TJ                                 | -40 to 125                                      | 00   |  |

| Storage Temperature Range                                               | T <sub>stg</sub>                   | -40 to 150                                      | - °C |  |

| Power Dissipation (Note a and b)                                        | P <sub>D</sub>                     | 830                                             | mW   |  |

| Thermal Impedance                                                       | θJA                                | 125                                             | °C/W |  |

| Lead Temperature (soldering 10 Sec)                                     |                                    | 300                                             | °C   |  |

- Notes

a. Device mounted with all leads soldered to P.C. Board

b. Derate 8.3 W/°C above 25°C

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| RECOMMENDED OPERATING CONDITIONS            |                   |              |      |  |  |

|---------------------------------------------|-------------------|--------------|------|--|--|

| Parameter                                   | Symbol            | Limit        | Unit |  |  |

| Bootstrap Voltage (High-Side Drain Voltage) | V <sub>BOOT</sub> | 4.5 to 30    |      |  |  |

| Logic Supply                                | $V_{DD}$          | 4.5 to 5.5   | V    |  |  |

| Bootstrap Capacitor                         | C <sub>BOOT</sub> | 100 n to 1 μ | F    |  |  |

| Ambient Temperature                         | T <sub>A</sub>    | -40 to 85    | °C   |  |  |

| SPECIFICATIONS                          |                       |                                                                         |                     |      |                       |      |  |

|-----------------------------------------|-----------------------|-------------------------------------------------------------------------|---------------------|------|-----------------------|------|--|

|                                         |                       | Test Conditions Unless Specified                                        | Limits              |      |                       |      |  |

| Parameter                               | Symbol                | $V_{BOOT}$ = 4.5 to 30 V, $V_{DD}$ = 4.5 to 5.5 V $T_{A}$ = -40 to 85°C | Mina                | Турь | Maxa                  | Unit |  |

| Power Supplies                          |                       |                                                                         |                     |      |                       |      |  |

| V <sub>DD</sub> Supply                  | $V_{DD}$              |                                                                         | 4.5                 |      | 5.5                   |      |  |

| I <sub>DD</sub> Supply                  | I <sub>DD1</sub> (en) | $SYN = H$ , $IN = H$ , $V_S = 0 V$                                      |                     |      | 1000                  |      |  |

| I <sub>DD</sub> Supply                  | I <sub>DD2(en)</sub>  | SYN = H, IN = L, $V_S = 0 \text{ V}$                                    |                     |      | 500                   | ١ .  |  |

| I <sub>DD</sub> Supply                  | I <sub>DD3(dis)</sub> | SYN = L, IN = X, V <sub>S</sub> = V                                     |                     |      | 500                   | μΑ   |  |

| I <sub>DD</sub> Supply                  | I <sub>DD4(en)</sub>  | SYN = H, IN = X, V <sub>S</sub> = 25 V, V <sub>BOOT</sub> = 30 V        |                     |      | 200                   |      |  |

| I <sub>DD</sub> Supply                  | I <sub>DD5(dis)</sub> | SYN = L, IN = X, $V_S = 25 \text{ V}$ , $V_{BOOT} = 30 \text{ V}$       |                     |      | 200                   |      |  |

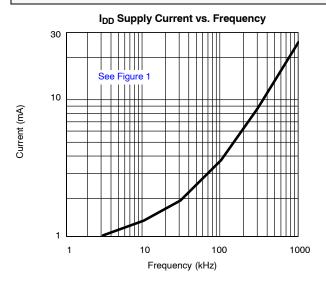

| I. Ouralis                              | I <sub>DD(en)</sub>   | F <sub>IN</sub> = 300 kHz, SYN = High, Driving Si4412DY                 |                     | 9    |                       |      |  |

| I <sub>DD</sub> Supply                  | I <sub>DD(dis)</sub>  | F <sub>IN</sub> = 300 kHz, SYN = Low, Driving Si4412DY                  |                     | 5    |                       | mA   |  |

| Boot Strap Current                      | I <sub>BOOT</sub>     | V <sub>BOOT</sub> = 30 V, V <sub>S</sub> = 25 V, V <sub>OUTH</sub> = H  | 0.9                 |      | 3                     |      |  |

| Reference Voltage                       | <u> </u>              |                                                                         |                     |      |                       |      |  |

| Break-Before-Make Reference Voltage     | $V_{BBM}$             |                                                                         | 1.1                 |      | 3                     | V    |  |

| Logic Inputs (SYN, IN)                  |                       |                                                                         |                     |      |                       |      |  |

| Input High                              | $V_{IH}$              |                                                                         | $0.7 \times V_{DD}$ |      | V <sub>DD</sub> + 0.3 | V    |  |

| Input Low                               | V <sub>IL</sub>       |                                                                         | -0.3                |      | 0.3×V <sub>DD</sub>   |      |  |

| Undervoltage Lockout                    |                       |                                                                         | 1                   |      | l.                    | I    |  |

| V <sub>DD</sub> Undervoltage            | $V_{UVL}$             | V <sub>DD</sub> Rising                                                  | 3.7                 |      | 4.3                   | Τ    |  |

| V <sub>DD</sub> Undervoltage Hysteresis | V <sub>HYST</sub>     |                                                                         |                     | 0.4  |                       | ٧    |  |

| SPECIFICATIONS                         |                        |                                                                                                        |        |      |      |      |  |

|----------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------|--------|------|------|------|--|

|                                        | Symbol                 | Test Conditions Unless Specified $V_{BOOT} = 4.5$ to 30 V, $V_{DD} = 4.5$ to 5.5 V $T_A = -40$ to 85°C | Limits |      |      |      |  |

| Parameter                              |                        |                                                                                                        | Mina   | Турь | Maxa | Unit |  |

| Bootstrap Diode                        | <u> </u>               |                                                                                                        |        |      |      |      |  |

| Diode Forward Voltage                  | VF <sub>D1</sub>       | Forward Current = 100 mA                                                                               |        | 0.8  | 1    | V    |  |

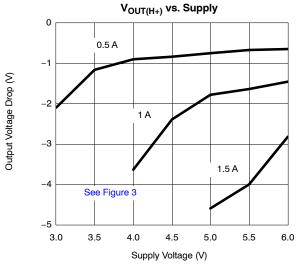

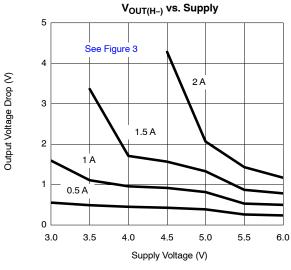

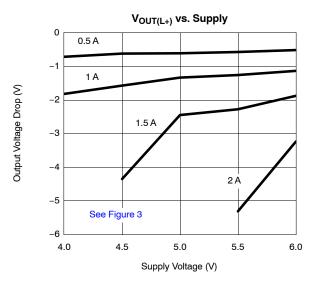

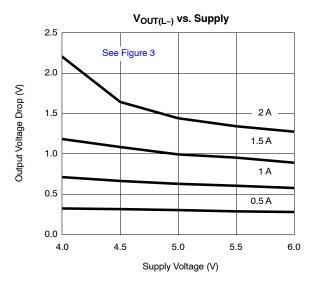

| Output Drive Current                   |                        |                                                                                                        | •      | •    | •    | •    |  |

| OUT <sub>H</sub> Source Current        | I <sub>OUT( H+)</sub>  | $V_{BOOT} - V_{S} = 3.7 \text{ V}, V_{OUTH} - V_{S} = 2 \text{ V}$                                     |        |      | -0.4 |      |  |

| OUT <sub>H</sub> Sink Current          | I <sub>OUT(H-)</sub>   | $V_{BOOT} - V_{S} = 3.7 \text{ V}, V_{OUTH} - V_{S} = 1 \text{ V}$                                     | 0.4    |      |      | 1    |  |

| OUT <sub>L</sub> Source Current        | I <sub>OUT (L+)</sub>  | V <sub>DD</sub> = 4.5 V, V <sub>OUTL</sub> = 2 V                                                       |        |      | -0.4 | A A  |  |

| OUT <sub>L</sub> Sink Current          | I <sub>OUT(L-)</sub>   | V <sub>DD</sub> = 4.5 V, V <sub>OUTL</sub> = 1 V                                                       | 0.6    |      |      |      |  |

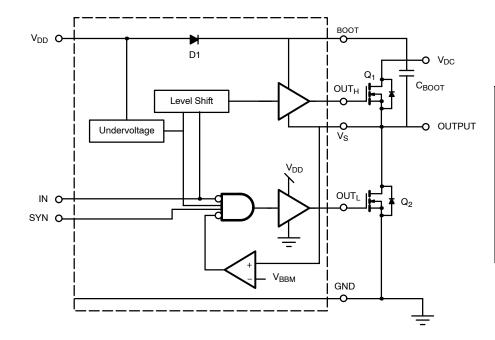

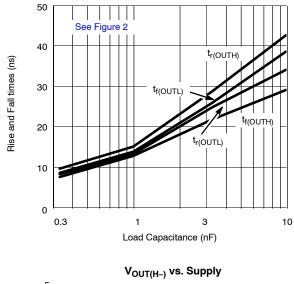

| Timing (C <sub>LOAD</sub> = 3 nF)      |                        |                                                                                                        |        |      |      |      |  |

| OUT <sub>L</sub> Off Propagation Delay | t <sub>pdl(OUTL)</sub> | V 45V                                                                                                  |        | 30   |      |      |  |

| OUT <sub>L</sub> On Propagation Delay  | t <sub>pdh(OUTL)</sub> | $V_{DD} = 4.5 \text{ V}$                                                                               |        | 20   |      | 1    |  |

| OUT <sub>H</sub> Off Propagation Delay | t <sub>pdl(OUTH)</sub> | V 45V                                                                                                  |        | 30   |      | 1    |  |

| OUT <sub>H</sub> On Propagation Delay  | t <sub>pdh(OUTH)</sub> | $V_{BOOT} - V_{S} = 4.5 V$                                                                             |        | 20   |      | 1    |  |

| OUT <sub>L</sub> Turn On Time          | t <sub>r(OUTL)</sub>   | OUT <sub>L</sub> = 10 to 90%                                                                           |        | 25   |      | ns   |  |

| OUT <sub>L</sub> Turn Off Time         | t <sub>f(OUTL)</sub>   | OUT <sub>L</sub> = 90 to 10%                                                                           |        | 25   |      | 1    |  |

| OUT <sub>H</sub> Turn On Time          | t <sub>r(OUTH)</sub>   | $OUT_H - V_S = 10 \text{ to } 90\%$                                                                    |        | 30   |      | 1    |  |

| OUT <sub>H</sub> Turn Off Time         | t <sub>f(OUTH)</sub>   | $OUT_H - V_S = 90 \text{ to } 10\%$                                                                    |        | 30   |      | 1    |  |

Notes

a. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

b. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

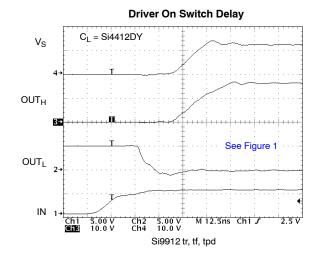

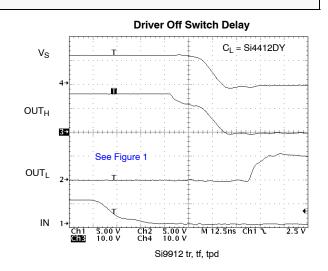

## **TIMING WAVEFORMS**

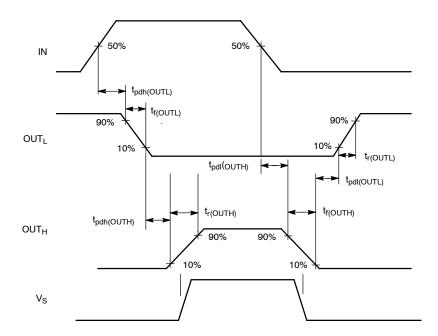

## **PIN CONFIGURATION**

| PIN DESCRIPTION |                  |                                                                                                                                    |  |  |

|-----------------|------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Number      | Name             | Function                                                                                                                           |  |  |

| 1               | OUT <sub>H</sub> | Output drive for upper MOSFET.                                                                                                     |  |  |

| 2               | GND              | Ground supply                                                                                                                      |  |  |

| 3               | IN               | CMOS level input signal. Controls both output drives.                                                                              |  |  |

| 4               | SYN              | Synchronous enable. When logic is high, the low-side driver is enabled.                                                            |  |  |

| 5               | OUT <sub>L</sub> | Output drive for lower MOSFET.                                                                                                     |  |  |

| 6               | $V_{DD}$         | Input power supply                                                                                                                 |  |  |

| 7               | BOOT             | Floating bootstrap supply for the upper MOSFET                                                                                     |  |  |

| 8               | V <sub>S</sub>   | Floating GND for the upper MOSFET. V <sub>S</sub> is connected to the buck switching node and the source side of the upper MOSFET. |  |  |

| ORDERING INFORMATION |             |                              |  |  |

|----------------------|-------------|------------------------------|--|--|

| Part Number          | Package     |                              |  |  |

| Si9913DY             |             | Bulk                         |  |  |

| Si9913DY-T1          | −40 to 85°C | Tape and Reel                |  |  |

| Si9913DY-T1—E3       |             | Lead (Pb)-Free Tape and Reel |  |  |

| Ī | Eval Kit | Temperature Range | Board Type    |  |

|---|----------|-------------------|---------------|--|

| ſ | Si9913DB | −40 to 85°C       | Surface Mount |  |

## **TYPICAL WAVEFORMS**

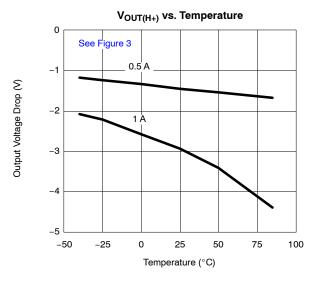

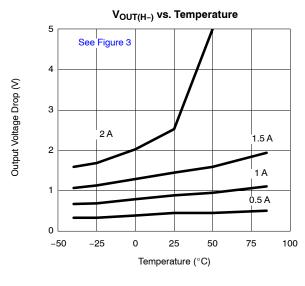

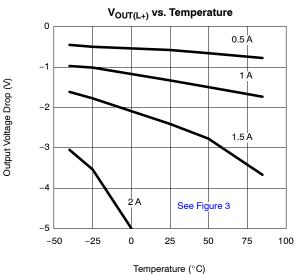

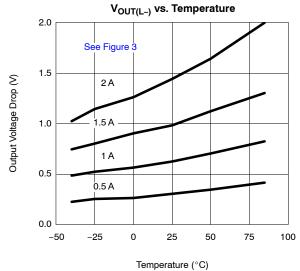

## TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

Rise and Fall Time vs. C<sub>LOAD</sub>

## TYPICAL CHARACTERISTICS (25°C UNLESS NOTED)

## THEORY OF OPERATION

### **Break-Before-Make Function**

The Si9913 has an internal break-before-make function to ensure that both high-side and low-side MOSFETs are not turned on at the same time. The high-side drive (OUT<sub>H</sub>) will not turn on until the low-side gate drive voltage (measured at the OUT<sub>L</sub> pin) is less than V<sub>BBM</sub>, thus ensuring that the low-side MOSFET is turned off. The low-side drive (OUT<sub>L</sub>) will not turn on until the voltage at the MOSFET half-bridge output (measured at the V<sub>S</sub> pin) is less than V<sub>BBM</sub>, thus ensuring that the high-side MOSFET is turned off.

## **Under Voltage Lockout Function**

The Si9913 has an internal under-voltage lockout feature to prevent driving the MOSFET gates when the supply voltage (at  $V_{DD}$ ) is less than the under-voltage lockout specification ( $V_{UVL}$ ). This prevents the output MOSFETs from being turned on without sufficient gate voltage to ensure they are fully on. There is hysteresis included in this feature to prevent lockout from cycling on and off.

# **Bootstrap Supply Operation** (see Functional Block Diagram)

The power to drive the high-side MOSFET (Q2) gate comes from the bootstrap capacitor ( $C_{BOOT}$ ). This capacitor charges through D1 during the time when the low-side MOSFET is on ( $V_S$  is at GND potential ), and then provides the necessary charge to turn on the high-side MOSFET.  $C_{BOOT}$  should be sized to be greater than ten times the high-side MOSFET gate capacitance, and large enough to supply the bootstrap current ( $I_{BOOT}$ ) during the high-side on time, without significant voltage droop.

## Synchronous Enable

The synchronous enable pin serves to enable and disable the drive to the low-side MOSFET gate. With SYN high, the low-side MOSFET is driven on and off in antiphase with the high-side MOSFET to form a synchronous rectifier. This improves efficiency at high load currents because the flyback current is carried by the MOSFET, thus eliminating the diode

drop. With SYN low, the low-side MOSFET is held off all the time. This is particularly useful for discontinuous operation under light load or pulse skipping mode, where there is a long off time, because it prevents current flowing back from the output to ground during the off time.

#### **Layout Considerations**

There are a few critical layout considerations for these parts. Firstly, the IC must be decoupled as closely as possible to the power pins. Secondly the IC should be placed physically close to the high- and low-side MOSFETs it is driving. The major consideration is that the MOSFET gates must be charged or discharged in a few nanoseconds, and the peak current to do this is of the order of 1 A. This current must flow from the decoupling and bootstrap capacitors to the IC, and from the output driver pin to the MOSFET gate, returning from the MOSFET source to the IC. The aim of the layout is to reduce the parasitic inductance of these current paths as much as possible. This is accomplished by making these traces as short as possible, and also running trace and its current return path adjacent to each other.

### **APPLICATIONS**

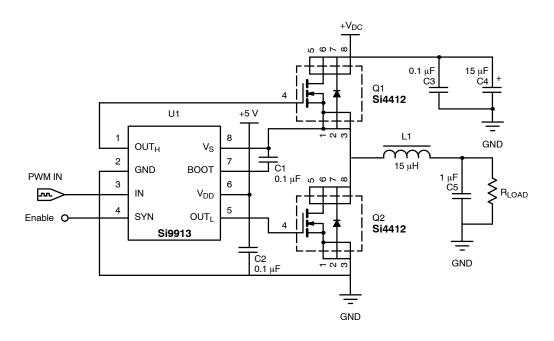

FIGURE 1. Typical Applications Schematic Circuit Used to Obtain Typical Rising and Falling Switching Waveforms

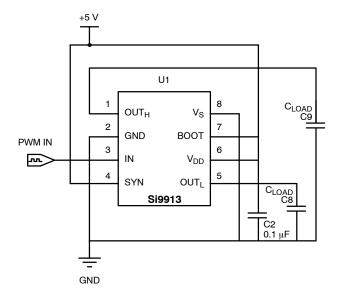

FIGURE 2. Capacitive Load Test Circuit Used to Measure Rise and Fall Times vs. Capacitance

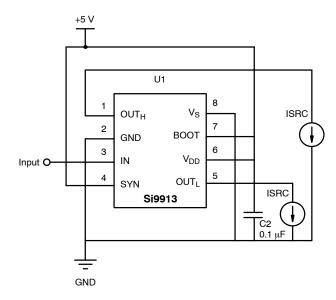

FIGURE 3. Load Test Schematic Circuit Used to Measure Driver Output Impedance

Vishay

## **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

Document Number: 91000 Revision: 18-Jul-08

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Vishay:

SI9913DY-E3