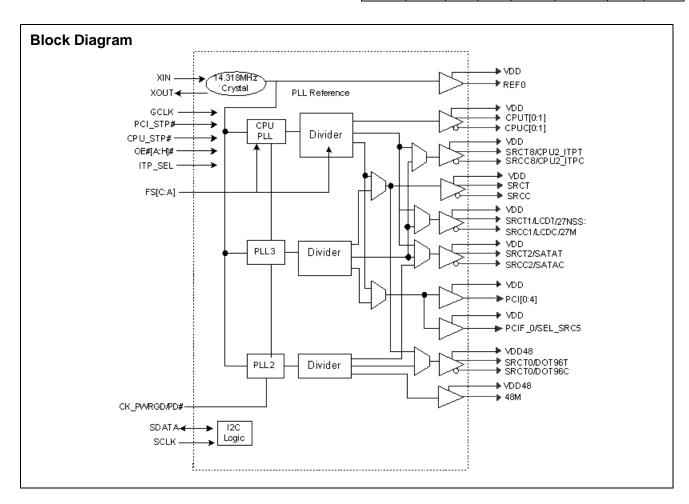

# Clock Generator for Intel®Mobile Chipset

#### **Features**

- Intel® CK505 Rev. 1.0 Compliant

- · Low power push-pull type differential output buffers

- · Integrated voltage regulator

- · Integrated resistors on differential clocks

- Scalable low voltage VDD\_IO (1.05V to 3.3V)

- 8-step programmable drive strength for single-ended clocks

- Differential CPU clocks with selectable frequency

- 100 MHz Differential SRC clocks

- 100 MHz Differential LCD clock

- 96 MHz Differential DOT clock

- 48 MHz USB clock

- 33 MHz PCI clocks

- 27 MHz Video clocks

- Buffered Reference Clock 14.318 MHz

- 14.318 MHz Crystal Input or Clock Input

- · Low-voltage frequency select input

- I<sup>2</sup>C support with readback capabilities

- Ideal Lexmark Spread Spectrum profile for maximum electromagnetic interference (EMI) reduction

- Industrial Temperature -40°C to 85°C

- 3.3V Power supply

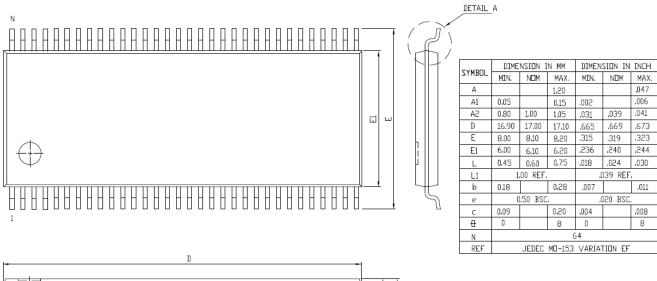

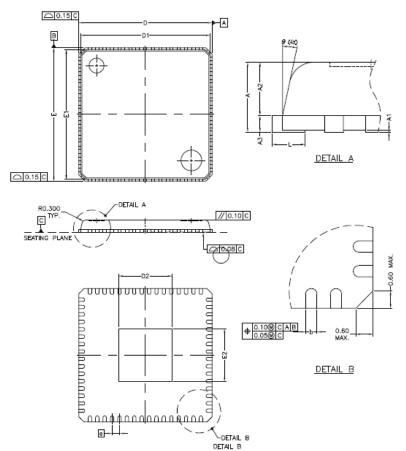

- 64-pin QFN and TSSOP packages

| CPU     | SRC   | PCI | REF | DOT96 | USB_48 | LCD | 27M |

|---------|-------|-----|-----|-------|--------|-----|-----|

| x2 / x3 | x8/12 | x6  | x 1 | x 1   | x 1    | x1  | x2  |

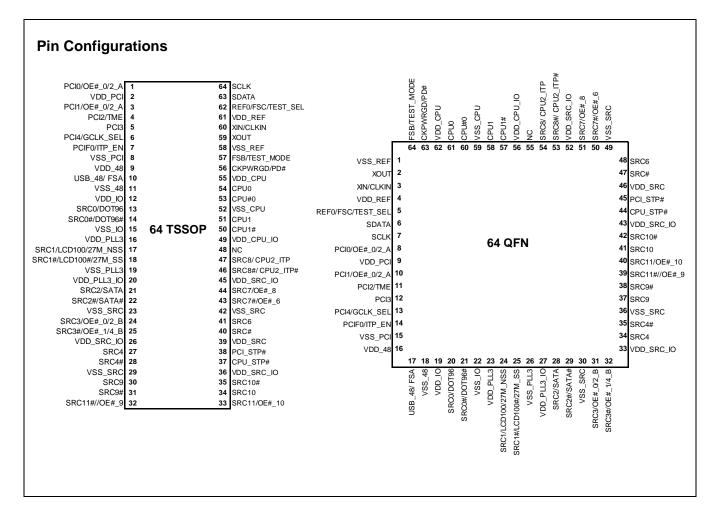

#### **64 QFN Pin Definitions**

| Pin No. | Name               | Туре          | Description                                                                                                                                                                                                                                                                                                   |  |

|---------|--------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | VSS_REF            | GND           | Ground for outputs.                                                                                                                                                                                                                                                                                           |  |

| 2       | XOUT               | O, SE         | 14.318MHz Crystal output. (Float XOUT if using CLKIN)                                                                                                                                                                                                                                                         |  |

| 3       | XIN/CLKIN          | I             | 14.318MHz Crystal input or 3.3V, 14.318MHz input clock signal.                                                                                                                                                                                                                                                |  |

| 4       | VDD_REF            | PWR           | 3.3V Power supply for outputs and also maintains SMBUS registers during power-down.                                                                                                                                                                                                                           |  |

| 5       | REF0/FSC/TEST_SEL  | I/O           | 3.3V tolerant input for CPU frequency selection/fixed 14.318MHz clock output. Selects test mode if pulled to V <sub>IHFS_C</sub> when CKPWRGD is asserted HIGH. <i>Refer to DC Electrical Specifications table for</i> V <sub>ILFS_C</sub> , V <sub>IMFS_C</sub> , V <sub>IHFS_C</sub> <i>specifications.</i> |  |

| 6       | SMB_DATA           | I/O           | SMBus compatible SDATA.                                                                                                                                                                                                                                                                                       |  |

| 7       | SMB_CLK            | I             | SMBus compatible SCLOCK.                                                                                                                                                                                                                                                                                      |  |

| 8       | PCI0/OE#_0/2_A     | I/O, SE       | 3.3V, 33MHz clock/3.3V OE# Input mappable via I2C to control either SRC0 or SRC2. (Default PCI0, 33MHz clock)                                                                                                                                                                                                 |  |

| 9       | VDD_PCI            | PWR           | 3.3V Power supply for PCI PLL.                                                                                                                                                                                                                                                                                |  |

| 10      | PCI1/OE#_1/4_A     | I/O, SE       | 3.3V, 33MHz clock/3.3V OE# Input mappable via I2C to control either SRC1 or SRC4. (Default PCI1, 33MHz clock)                                                                                                                                                                                                 |  |

| 11      | PCI2/TME           | I/O, SE       | 3.3V tolerance input for overclocking enable pin/3.3V, 33MHz clock. (Refer to DC Electrical Specifications table for Vil_FS and Vih_FS specifications)                                                                                                                                                        |  |

| 12      | PCI3               | O, SE,        | 33 MHz clock.                                                                                                                                                                                                                                                                                                 |  |

| 13      | PCI4 / GCLK_SEL    | I/O, SE       | 33 MHz clock output/3.3V-tolerant input for selecting graphic clock source on pin 13, 14, 17and 18 Sampled on CKPWRGD assertion  GCLK_SEL Pin13 Pin14 Pin17 Pin 18  0 DOT96T DOT96C SRC1T/LCD_100T SRC1C/LCD_100C  1 SRCT0 SRCC0 27M_NSS 27M_SS                                                               |  |

| 14      | PCIF_0/ITP_EN      | I/O, SE       | 3.3V LVTTL input to enable SRC8 or CPU2_ITP/33 MHz clock output. (sampled on the CK_PWRGD assertion) 1 = CPU2_ITP, 0 = SRC8                                                                                                                                                                                   |  |

| 15      | VSS_PCI            | GND           | Ground for outputs.                                                                                                                                                                                                                                                                                           |  |

| 16      | VDD_48             | PWR           | 3.3V Power supply for outputs and PLL.                                                                                                                                                                                                                                                                        |  |

| 17      | USB_48/FSA         | I/O           | 3.3V tolerant input for CPU frequency selection/fixed 3.3V, 48MHz clock output. (Refer to DC Electrical Specifications table for Vil_FS and Vih_FS specifications)                                                                                                                                            |  |

| 18      | VSS_48             | GND           | Ground for outputs.                                                                                                                                                                                                                                                                                           |  |

| 19      | VDD_IO             | PWR           | 0.7V Power supply for outputs.                                                                                                                                                                                                                                                                                |  |

| 20      | SRC0/DOT96         | O, DIF        | 100MHz Differential serial reference clocks/Fixed 96MHz clock output. (Selected via I2C default is SRC0)                                                                                                                                                                                                      |  |

| 21      | SRC0#/DOT96#       | O, DIF        | 100MHz Differential serial reference clocks/Fixed 96MHz clock output. (Selected via I2C default is SRC0)                                                                                                                                                                                                      |  |

| 22      | VSS_IO             | GND           | Ground for PLL2.                                                                                                                                                                                                                                                                                              |  |

| 23      | VDD_PLL3           | PWR           | 3.3V Power supply for PLL3                                                                                                                                                                                                                                                                                    |  |

| 24      | SRC1/LCD100/27_NSS | O, DIF,<br>SE | True 100 MHz differential serial reference clock output/True 100 MHz LCD video clock output / Non-spread 27-MHz video clock output. Selected via GCLK_SEL at CKPWRGD assertion.                                                                                                                               |  |

| 25      | SRC1#/LCD100#27_SS | O, DIF,<br>SE | Complementary 100 MHz differential serial reference clock output/Complementary 100 MHz LCD video clock output /Spread 27 MHz video clock output. Selected via GCLK_SEL at CKPWRGD assertion.                                                                                                                  |  |

| 26      | VSS_PLL3           | GND           | Ground for PLL3.                                                                                                                                                                                                                                                                                              |  |

|         |                    |               |                                                                                                                                                                                                                                                                                                               |  |

## 64 QFN Pin Definitions (continued)

| Pin No. | Name             | Туре        | Description                                                                                                                                                                                                                   |  |

|---------|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 27      | VDD_PLL3_IO      | PWR         | IO Power supply for PLL3 outputs.                                                                                                                                                                                             |  |

| 28      | SRC2/SATA        | O, DIF      | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 29      | SRC2#/SATA#      | O, DIF      | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 30      | VSS_SRC          | GND         | Ground for outputs.                                                                                                                                                                                                           |  |

| 31      | SRC3/OE#_0/2_B   | I/O,<br>Dif | 100MHz Differential serial reference clocks / 3.3V OE#_0/2_B, input, mappable via I2C to control either SRC0 or SRC2. (Default SRC3, 100MHz clock)                                                                            |  |

| 32      | SRC3#OE#_1/4_B   | I/O,<br>Dif | 100MHz Differential serial reference clocks / 3.3V OE#_1/4_B input, mappable via I2C to control either SRC1 or SRC4. (Default SRC3, 100MHz clock)                                                                             |  |

| 33      | VDD_SRC_IO       | PWR         | IO power supply for SRC outputs.                                                                                                                                                                                              |  |

| 34      | SRC4             | O, DIF      | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 35      | SRC4#            | O, DIF      | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 36      | VSS_SRC          | GND         | Ground for outputs.                                                                                                                                                                                                           |  |

| 37      | SRC9             | O, DIF      | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 38      | SRC9#            | O, DIF      | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 39      | SRC11#/OE#_9     | I/O,<br>Dif | 100MHz Differential serial reference clocks/3.3V OE#9 Input controlling SRC9 (Default SRC11, 100MHz clock)                                                                                                                    |  |

| 40      | SRC11/OE#_10     | I/O,<br>Dif | 100MHz Differential serial reference clocks/3.3V OE#10 Input controlling SRC10. (Default SRC11, 100MHz clock)                                                                                                                 |  |

| 41      | SRC10            | O, DIF      | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 42      | SRC10#           | O, DIF      | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 43      | VDD_SRC_IO       | PWR         | IO Power supply for SRC outputs.                                                                                                                                                                                              |  |

| 44      | CPU_STP#         | I           | 3.3V tolerant input for stopping CPU outputs                                                                                                                                                                                  |  |

| 45      | PCI_STP#         | I           | 3.3V tolerant input for stopping PCI and SRC outputs                                                                                                                                                                          |  |

| 46      | VDD_SRC          | PWR         | 3.3V Power supply for SRC PLL.                                                                                                                                                                                                |  |

| 47      | SRC6#            | O, DIF      | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 48      | SRC6             | O, DIF      | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 49      | VSS_SRC          | GND         | Ground for outputs.                                                                                                                                                                                                           |  |

| 50      | SRC7#/OE#_6      | I/O,<br>Dif | 100MHz Differential serial reference clocks/3.3V OE#6 Input controlling SRC6. (Default SRC7, 100MHz clock).                                                                                                                   |  |

| 51      | SRC7/OE#_8       | I/O,<br>Dif | 100MHz Differential serial reference clocks/3.3V OE#8 Input controlling SRC8. (Default SRC7, 100MHz clock).                                                                                                                   |  |

| 52      | VDD_SRC_IO       | PWR         | 0.7V power supply for SRC outputs.                                                                                                                                                                                            |  |

| 53      | SRC8#/CPU2#_ITP# | O, DIF      | Selectable differential CPU or SRC clock output. ITP_EN = 0 at CKPWRGD assertion = SRC8 ITP_EN = 1 @ CKPWRGD assertion = CPU2 (Note: CPU2 is an iAMT clock in iAMT mode depending on the configuration set in Byte 11 Bit3:2) |  |

| 54      | SRC8/CPU2_ITP    | O, DIF      | Selectable differential CPU or SRC clock output. ITP_EN = 0 at CKPWRGD assertion = SRC8 ITP_EN = 1 @ CKPWRGD assertion = CPU2 (Note: CPU2 is an iAMT clock in iAMT mode depending on the configuration set in Byte 1: Bit3:2) |  |

| 55      | NC               | NC          | No Connect                                                                                                                                                                                                                    |  |

| 56      | VDD_CPU_IO       | PWR         | IO Power supply for CPU outputs.                                                                                                                                                                                              |  |

| 57      | CPU1#            | O, DIF      | Differential CPU clock outputs. (Note: CPU1 is an iAMT clock in iAMT mode depending on the configuration set in Byte 11 Bit3:2)                                                                                               |  |

| 58      | CPU1             | O, DIF      | Differential CPU clock outputs. (Note: CPU1 is an iAMT clock in iAMT mode depending on the configuration set in Byte 11 Bit3:2)                                                                                               |  |

| 59      | VSS_CPU          | GND         | Ground for outputs.                                                                                                                                                                                                           |  |

## 64 QFN Pin Definitions (continued)

| Pin No. | Name          | Туре   | Description                                                                                                                                                                                                                             |

|---------|---------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 60      | CPU#0         | O, DIF | Differential CPU clock outputs.                                                                                                                                                                                                         |

| 61      | CPU0          | O, DIF | Differential CPU clock outputs.                                                                                                                                                                                                         |

| 62      | VDD_CPU       | PWR    | 3.3V Power supply for CPU PLL.                                                                                                                                                                                                          |

| 63      | CKPWRGD/PD#   | I      | 3.3V LVTTL input. This pin is a level sensitive strobe used to latch the FS_A, FS_B, FS_C, FS_D, SRC5_SEL, and ITP_EN. After CKPWRGD (active HIGH) assertion, this pin becomes a real-time input for asserting power down (active LOW). |

| 64      | FSB/TEST_MODE | I      | 3.3V tolerant input for CPU frequency selection. Selects Ref/N or Tri-state when in test mode 0 = Tri-state, 1 = Ref/N. Refer to DC Electrical Specifications table for Vil_FS and Vih_FS specifications.                               |

## **64 TSSOP Pin Definition**

| Pin No. | Name            | Туре    | Description                                                                                                                                                        |  |  |  |  |

|---------|-----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1       | PCI0/OE#_0/2_A  | I/O, SE | 3.3V, 33MHz clock/3.3V OE# Input mappable via I2C to control either SRC0 or SRC2. (Default PCI0, 33MHz clock)                                                      |  |  |  |  |

| 2       | VDD_PCI         | PWR     | 3.3V Power supply for PCI PLL.                                                                                                                                     |  |  |  |  |

| 3       | PCI1/OE#_1/4_A  | I/O, SE | 3.3V, 33MHz clock/3.3V OE# Input mappable via I2C to control either SRC1 or SRC4. (Default PCI1, 33MHz clock)                                                      |  |  |  |  |

| 4       | PCI2/TME        | I/O, SE | 3.3V tolerance input for overclocking enable pin/3.3V, 33MHz clock. (Refer to DC Electrical Specifications table for Vil_FS and Vih_FS specifications)             |  |  |  |  |

| 5       | PCI3            | O, SE,  | 33 MHz clock.                                                                                                                                                      |  |  |  |  |

| 6       | PCI4 / GCLK_SEL | I/O, SE | 33 MHz clock output/3.3V-tolerant input for selecting graphic clock source on pin 13, 14, 17and 18 Sampled on CKPWRGD assertion                                    |  |  |  |  |

|         |                 |         | GCLK_SEL Pin13 Pin14 Pin17 Pin 18                                                                                                                                  |  |  |  |  |

|         |                 |         | 0 DOT96T DOT96C SRC1T/LCD_100T SRC1C/LCD_100C                                                                                                                      |  |  |  |  |

|         |                 |         | 1 SRCT0 SRCC0 27M_NSS 27M_SS                                                                                                                                       |  |  |  |  |

| 7       | PCIF_0/ITP_EN   | I/O, SE | 3.3V LVTTL input to enable SRC8 or CPU2_ITP/33 MHz clock output. (sampled on the CK_PWRGD assertion) 1 = CPU2_ITP, 0 = SRC8                                        |  |  |  |  |

| 8       | VSS_PCI         | GND     | Ground for outputs.                                                                                                                                                |  |  |  |  |

| 9       | VDD_48          | PWR     | 3.3V Power supply for outputs and PLL.                                                                                                                             |  |  |  |  |

| 10      | USB_48/FSA      | I/O     | 3.3V tolerant input for CPU frequency selection/fixed 3.3V, 48MHz clock output. (Refer to DC Electrical Specifications table for Vil_FS and Vih_FS specifications) |  |  |  |  |

| 11      | VSS_48          | GND     | Ground for outputs.                                                                                                                                                |  |  |  |  |

| 12      | VDD_IO          | PWR     | 0.7V Power supply for outputs.                                                                                                                                     |  |  |  |  |

| 13      | SRC0/DOT96      | O, DIF  | 100MHz Differential serial reference clocks/Fixed 96MHz clock output. (Selected via I2C default is SRC0)                                                           |  |  |  |  |

| 14      | SRC0#/DOT96#    | O, DIF  | 100MHz Differential serial reference clocks/Fixed 96MHz clock output. (Selected via I2C default is SRC0)                                                           |  |  |  |  |

| 15      | VSS_IO          | GND     | Ground for PLL2.                                                                                                                                                   |  |  |  |  |

| 16      | VDD_PLL3        | PWR     | 3.3V Power supply for PLL3                                                                                                                                         |  |  |  |  |

...... DOC #: SP-AP-0063 (Rev. AA) Page 5 of 31

## 64 TSSOP Pin Definition (continued)

| Pin No. | Name                | Туре          | Description                                                                                                                                                                                                                   |  |

|---------|---------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 17      | SRC1/LCD100/27_NSS  | O, DIF,<br>SE | True 100 MHz differential serial reference clock output/True 100 MHz LCD video clock output / Non-spread 27-MHz video clock output. Selected via GCLK_SEL at CKPWRGD assertion.                                               |  |

| 18      | SRC1#/LCD100#/27_SS | O, DIF,<br>SE | Complementary 100 MHz differential serial reference clock output/Complementary 100 MHz LCD video clock output /Spread 27 MHz video clock output. Selected via GCLK_SEL at CKPWRGD assertion.                                  |  |

| 19      | VSS_PLL3            | GND           | Ground for PLL3.                                                                                                                                                                                                              |  |

| 20      | VDD_PLL3_IO         | PWR           | IO Power supply for PLL3 outputs.                                                                                                                                                                                             |  |

| 21      | SRC2/SATA           | O, DIF        | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 22      | SRC2#/SATA#         | O, DIF        | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 23      | VSS_SRC             | GND           | Ground for outputs.                                                                                                                                                                                                           |  |

| 24      | SRC3/OE#_0/2_B      | I/O,<br>Dif   | 100MHz Differential serial reference clocks / 3.3V OE#_0/2_B, input, mappable via I2C to control either SRC0 or SRC2. (Default SRC3, 100MHz clock)                                                                            |  |

| 25      | SRC3#0E#_1/4_B      | I/O,<br>Dif   | 100MHz Differential serial reference clocks / 3.3V OE#_1/4_B input, mappable via I2C to control either SRC1 or SRC4. (Default SRC3, 100MHz clock)                                                                             |  |

| 26      | VDD_SRC_IO          | PWR           | IO power supply for SRC outputs.                                                                                                                                                                                              |  |

| 27      | SRC4                | O, DIF        | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 28      | SRC4#               | O, DIF        | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 29      | VSS_SRC             | GND           | Ground for outputs.                                                                                                                                                                                                           |  |

| 30      | SRC9                | O, DIF        | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 31      | SRC9#               | O, DIF        | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 32      | SRC11#/OE#_9        | I/O,<br>Dif   | 100MHz Differential serial reference clocks/3.3V OE#9 Input controlling SRC9 (Default SRC11, 100MHz clock)                                                                                                                    |  |

| 33      | SRC11/OE#_10        | I/O,<br>Dif   | 100MHz Differential serial reference clocks/3.3V OE#10 Input controlling SRC10. (Default SRC11, 100MHz clock)                                                                                                                 |  |

| 34      | SRC10               | O, DIF        | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 35      | SRC10#              | O, DIF        | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 36      | VDD_SRC_IO          | PWR           | IO Power supply for SRC outputs.                                                                                                                                                                                              |  |

| 37      | CPU_STP#            | I             | 3.3V tolerant input for stopping CPU outputs                                                                                                                                                                                  |  |

| 38      | PCI_STP#            | I             | 3.3V tolerant input for stopping PCI and SRC outputs                                                                                                                                                                          |  |

| 39      | VDD_SRC             | PWR           | 3.3V Power supply for SRC PLL.                                                                                                                                                                                                |  |

| 40      | SRC6#               | O, DIF        | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 41      | SRC6                | O, DIF        | 100MHz Differential serial reference clocks.                                                                                                                                                                                  |  |

| 42      | VSS_SRC             | GND           | Ground for outputs.                                                                                                                                                                                                           |  |

| 43      | SRC7#/OE#_6         | I/O,<br>Dif   | 100MHz Differential serial reference clocks/3.3V OE#6 Input controlling SRC6. (Default SRC7, 100MHz clock).                                                                                                                   |  |

| 44      | SRC7/OE#_8          | I/O,<br>Dif   | 100MHz Differential serial reference clocks/3.3V OE#8 Input controlling SRC8. (Default SRC7, 100MHz clock).                                                                                                                   |  |

| 45      | VDD_SRC_IO          | PWR           | 0.7V power supply for SRC outputs.                                                                                                                                                                                            |  |

| 46      | SRC8#/CPU2#_ITP#    | O, DIF        | Selectable differential CPU or SRC clock output. ITP_EN = 0 at CKPWRGD assertion = SRC8 ITP_EN = 1 @ CKPWRGD assertion = CPU2 (Note: CPU2 is an iAMT clock in iAMT mode depending on the configuration set in Byte 1 Bit3:2)  |  |

| 47      | SRC8/CPU2_ITP       | O, DIF        | Selectable differential CPU or SRC clock output. ITP_EN = 0 at CKPWRGD assertion = SRC8 ITP_EN = 1 @ CKPWRGD assertion = CPU2 (Note: CPU2 is an iAMT clock in iAMT mode depending on the configuration set in Byte 11 Bit3:2) |  |

#### 64 TSSOP Pin Definition (continued)

| Pin No. | Name              | Туре   | Description                                                                                                                                                                                                                                                                                            |  |

|---------|-------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 48      | NC                | NC     | No Connect                                                                                                                                                                                                                                                                                             |  |

| 49      | VDD_CPU_IO        | PWR    | IO Power supply for CPU outputs.                                                                                                                                                                                                                                                                       |  |

| 50      | CPU1#             | O, DIF | Differential CPU clock outputs. (Note: CPU1 is an iAMT clock in iAMT mode depending on the configuration set in Byte 11 Bit3:2)                                                                                                                                                                        |  |

| 51      | CPU1              | O, DIF | Differential CPU clock outputs. (Note: CPU1 is an iAMT clock in iAMT mode depending on the configuration set in Byte 11 Bit3:2)                                                                                                                                                                        |  |

| 52      | VSS_CPU           | GND    | Ground for outputs.                                                                                                                                                                                                                                                                                    |  |

| 53      | CPU#0             | O, DIF | Differential CPU clock outputs.                                                                                                                                                                                                                                                                        |  |

| 54      | CPU0              | O, DIF | Differential CPU clock outputs.                                                                                                                                                                                                                                                                        |  |

| 55      | VDD_CPU           | PWR    | 3.3V Power supply for CPU PLL.                                                                                                                                                                                                                                                                         |  |

| 56      | CKPWRGD/PD#       | I      | 3.3V LVTTL input. This pin is a level sensitive strobe used to latch the FS_A, FS_FS_C, FS_D, SRC5_SEL, and ITP_EN.  After CKPWRGD (active HIGH) assertion, this pin becomes a real-time input f asserting power down (active LOW).                                                                    |  |

| 57      | FSB/TEST_MODE     | I      | 3.3V tolerant input for CPU frequency selection. Selects Ref/N or Tri-state when in test mode 0 = Tri-state, 1 = Ref/N. Refer to DC Electrical Specifications table for Vil_FS and Vih_FS specifications.                                                                                              |  |

| 58      | VSS_REF           | GND    | Ground for outputs.                                                                                                                                                                                                                                                                                    |  |

| 59      | XOUT              | O, SE  | 14.318MHz Crystal output. (Float XOUT if using CLKIN)                                                                                                                                                                                                                                                  |  |

| 60      | XIN/CLKIN         | I      | 14.318MHz Crystal input or 3.3V, 14.318MHz input clock signal.                                                                                                                                                                                                                                         |  |

| 61      | VDD_REF           | PWR    | 3.3V Power supply for outputs and also maintains SMBUS registers during power-down.                                                                                                                                                                                                                    |  |

| 62      | REF0/FSC/TEST_SEL | I/O    | 3.3V tolerant input for CPU frequency selection/fixed 14.318MHz clock output. Selects test mode if pulled to V <sub>IHFS_C</sub> when CKPWRGD is asserted HIGH. <i>Refer to DC Electrical Specifications table for</i> V <sub>ILFS_C</sub> , V <sub>IMFS_C</sub> , V <sub>IHFS_C</sub> specifications. |  |

| 63      | SMB_DATA          | I/O    | SMBus compatible SDATA.                                                                                                                                                                                                                                                                                |  |

| 64      | SMB_CLK           | I      | SMBus compatible SCLOCK.                                                                                                                                                                                                                                                                               |  |

Table 1. Frequency Select Pin (FSA, FSB and FSC)

| FSC | FSB | FSA | CPU      | SRC      | PCIF/PCI | 27MHz    | REF        | DOT96    | USB      |

|-----|-----|-----|----------|----------|----------|----------|------------|----------|----------|

| 0   | 0   | 0   | 266 MHz  |          |          |          |            |          |          |

| 0   | 0   | 1   | 133 MHz  |          |          |          |            |          |          |

| 0   | 1   | 0   | 200 MHz  |          |          |          |            |          |          |

| 0   | 1   | 1   | 166 MHz  | 100 MHz  | 33 MHz   | 27 MHz   | 14.318 MHz | 96 MHz   | 48 MHz   |

| 1   | 0   | 0   | 333 MHz  |          |          |          |            |          |          |

| 1   | 0   | 1   | 100 MHz  |          |          |          |            |          |          |

| 1   | 1   | 0   | 400 MHz  |          |          |          |            |          |          |

| 1   | 1   | 1   | Reserved | Reserved | Reserved | Reserved | Reserved   | Reserved | Reserved |

#### Frequency Select Pin (FSA, FSB and FSC)

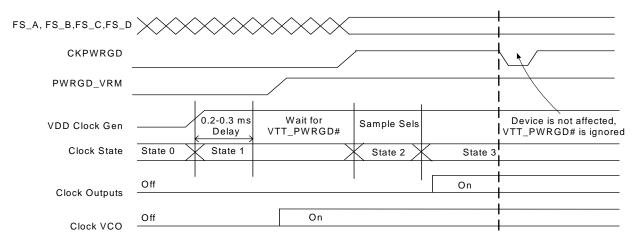

Apply the appropriate logic levels to FSA, FSB, and FSC inputs before CKPWRGD assertion to achieve host clock frequency selection. When the clock chip sampled HIGH on CKPWRGD and indicates that VTT voltage is stable then FSA, FSB, and FSC input values are sampled. This process

employs a one-shot functionality and once the CKPWRGD sampled a valid HIGH, all other FSA, FSB, FSC, and CKPWRGD transitions are ignored except in test mode.

#### **Serial Data Interface**

To enhance the flexibility and function of the clock synthesizer, a two-signal serial interface is provided. Through the Serial Data Interface, various device functions, such as individual

clock output buffers are individually enabled or disabled. The registers associated with the Serial Data Interface initialize to

their default setting at power-up. The use of this interface is optional. Clock device register changes are normally made at system initialization, if any are required. The interface cannot be used during system operation for power management functions.

#### **Data Protocol**

The clock driver serial protocol accepts byte write, byte read, block write, and block read operations from the controller. For

block write/read operation, access the bytes in sequential order from lowest to highest (most significant bit first) with the ability to stop after any complete byte is transferred. For byte write and byte read operations, the system controller can access individually indexed bytes. The offset of the indexed byte is encoded in the command code described in *Table 2*.

The block write and block read protocol is outlined in *Table 3* while *Table 4* outlines byte write and byte read protocol. The slave receiver address is 11010010 (D2h).

#### **Table 2. Command Code Definition**

| Bit   | Description                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------|

| 7     | 0 = Block read or block write operation, 1 = Byte read or byte write operation                                              |

| (6:0) | Byte offset for byte read or byte write operation. For block read or block write operations, these bits should be '0000000' |

Table 3. Block Read and Block Write Protocol

|       | Block Write Protocol          |       | Block Read Protocol                 |  |  |

|-------|-------------------------------|-------|-------------------------------------|--|--|

| Bit   | Description                   | Bit   | Description                         |  |  |

| 1     | Start                         | 1     | Start                               |  |  |

| 8:2   | Slave address–7 bits          | 8:2   | Slave address–7 bits                |  |  |

| 9     | Write                         | 9     | Write                               |  |  |

| 10    | Acknowledge from slave        | 10    | Acknowledge from slave              |  |  |

| 18:11 | Command Code–8 bits           | 18:11 | Command Code–8 bits                 |  |  |

| 19    | Acknowledge from slave        | 19    | Acknowledge from slave              |  |  |

| 27:20 | Byte Count–8 bits             | 20    | Repeat start                        |  |  |

| 28    | Acknowledge from slave        | 27:21 | Slave address–7 bits                |  |  |

| 36:29 | Data byte 1–8 bits            | 28    | Read = 1                            |  |  |

| 37    | Acknowledge from slave        | 29    | Acknowledge from slave              |  |  |

| 45:38 | Data byte 2–8 bits            | 37:30 | Byte Count from slave–8 bits        |  |  |

| 46    | Acknowledge from slave        | 38    | Acknowledge                         |  |  |

|       | Data Byte /Slave Acknowledges | 46:39 | Data byte 1 from slave–8 bits       |  |  |

|       | Data Byte N–8 bits            | 47    | Acknowledge                         |  |  |

|       | Acknowledge from slave        | 55:48 | Data byte 2 from slave–8 bits       |  |  |

|       | Stop                          | 56    | Acknowledge                         |  |  |

|       |                               |       | Data bytes from slave / Acknowledge |  |  |

|       |                               |       | Data Byte N from slave–8 bits       |  |  |

|       |                               |       | NOT Acknowledge                     |  |  |

|       |                               |       | Stop                                |  |  |

Table 4. Byte Read and Byte Write Protocol

|       | Byte Write Protocol    |       | Byte Read Protocol     |

|-------|------------------------|-------|------------------------|

| Bit   | Description            | Bit   | Description            |

| 1     | Start                  | 1     | Start                  |

| 8:2   | Slave address–7 bits   | 8:2   | Slave address–7 bits   |

| 9     | Write                  | 9     | Write                  |

| 10    | Acknowledge from slave | 10    | Acknowledge from slave |

| 18:11 | Command Code–8 bits    | 18:11 | Command Code–8 bits    |

| 19    | Acknowledge from slave | 19    | Acknowledge from slave |

#### Table 4. Byte Read and Byte Write Protocol

| 27:20 | Data byte–8 bits       | 20    | Repeated start         |

|-------|------------------------|-------|------------------------|

| 28    | Acknowledge from slave | 27:21 | Slave address–7 bits   |

| 29    | Stop                   | 28    | Read                   |

|       |                        | 29    | Acknowledge from slave |

|       |                        | 37:30 | Data from slave–8 bits |

|       |                        | 38    | NOT Acknowledge        |

|       |                        | 39    | Stop                   |

#### **Control Registers**

#### Byte 0: Control Register 0

| Bit | @Pup | Name         | Description                                                                                                                  |

|-----|------|--------------|------------------------------------------------------------------------------------------------------------------------------|

| 7   | HW   | FS_C         | CPU Frequency Select Bit, set by HW                                                                                          |

| 6   | HW   | FS_B         | CPU Frequency Select Bit, set by HW                                                                                          |

| 5   | HW   | FS_A         | CPU Frequency Select Bit, set by HW                                                                                          |

| 4   | 0    | iAMT_EN      | Set via SMBus or by combination of PWRDWN, CPU_STP, and PCI_STP 0 = Legacy Mode, 1 = iAMT Enabled                            |

| 3   | 0    | Reserved     | Reserved                                                                                                                     |

| 2   | 0    | SRC_Main_SEL | Select source for SRC clock  0 = SRC_MAIN = PLL1, PLL3_CFG Table applies  1 = SRC_MAIN = PLL3, PLL3_CFG Table does not apply |

| 1   | 0    | SATA_SEL     | Select source of SATA clock 0 = SATA = SRC_MAIN, 1= SATA = PLL2                                                              |

| 0   | 1    | PD_Restore   | Save configuration when PD# is asserted 0 = Config. cleared, 1 = Config. saved                                               |

## Byte 1: Control Register 1

| Bit | @Pup | Name       | Description                                                                                                 |

|-----|------|------------|-------------------------------------------------------------------------------------------------------------|

| 7   | 0    | SRC0_SEL   | Select for SRC0 or DOT96 0 = SRC0, 1 = DOT96 When GCLK_SEL=0, this bit is 1. When GCLK_SEL=1, this bit is 0 |

| 6   | 0    | PLL1_SS_DC | Select for down or center SS<br>0 = Down spread, 1 = Center spread                                          |

| 5   | 0    | PLL3_SS_DC | Select for down or center SS<br>0 = Down spread, 1 = Center spread                                          |

| 4   | 0    | PLL3_CFB3  | Bit 4:1 only applies when SRC_Main_SEL = 0                                                                  |

| 3   | 0    | PLL3_CFB2  | See Table 8: PLL3 / SE configuration table                                                                  |

| 2   | 1    | PLL3_CFB1  |                                                                                                             |

| 1   | 0    | PLL3_CFB0  |                                                                                                             |

| 0   | 1    | Reserved   | Reserved                                                                                                    |

#### Byte 2: Control Register 2

| Bit | @Pup | Name  | Description                                                     |

|-----|------|-------|-----------------------------------------------------------------|

| 7   | 1    | REF   | Output enable for REF 0 = Output Disabled, 1 = Output Enabled   |

| 6   | 1    | USB   | Output enable for USB 0 = Output Disabled, 1 = Output Enabled   |

| 5   | 1    | PCIF0 | Output enable for PCIF0 0 = Output Disabled, 1 = Output Enabled |

...... DOC #: SP-AP-0063 (Rev. AA) Page 9 of 31

Byte 2: Control Register 2 (continued)

| Bit | @Pup | Name | Description                                                    |

|-----|------|------|----------------------------------------------------------------|

| 4   | 1    | PCI4 | Output enable for PCI4 0 = Output Disabled, 1 = Output Enabled |

| 3   | 1    | PCI3 | Output enable for PCI3 0 = Output Disabled, 1 = Output Enabled |

| 2   | 1    | PCI2 | Output enable for PCl2 0 = Output Disabled, 1 = Output Enabled |

| 1   | 1    | PCI1 | Output enable for PCI1 0 = Output Disabled, 1 = Output Enabled |

| 0   | 1    | PCI0 | Output enable for PCI0 0 = Output Disabled, 1 = Output Enabled |

## Byte 3: Control Register 3

| Bit | @Pup | Name               | Description                                                                |

|-----|------|--------------------|----------------------------------------------------------------------------|

| 7   | 1    | SRC[T/C]11         | Output enable for SRC11<br>0 = Output Disabled, 1 = Output Enabled         |

| 6   | 1    | SRC[T/C]10         | Output enable for SRC10<br>0 = Output Disabled, 1 = Output Enabled         |

| 5   | 1    | SRC[T/C]9          | Output enable for SRC9 0 = Output Disabled, 1 = Output Enabled             |

| 4   | 1    | SRC[T/C]8/CPU2_ITP | Output enable for SRC8 or CPU2_ITP 0 = Output Disabled, 1 = Output Enabled |

| 3   | 1    | SRC[T/C]7          | Output enable for SRC7<br>0 = Output Disabled, 1 = Output Enabled          |

| 2   | 1    | SRC[T/C]6          | Output enable for SRC6<br>0 = Output Disabled, 1 = Output Enabled          |

| 1   | 1    | Reserved           | Reserved                                                                   |

| 0   | 1    | SRC[T/C]4          | Output enable for SRC4<br>0 = Output Disabled, 1 = Output Enabled          |

#### Byte 4: Control Register 4

| Bit | @Pup | Name                    | Description                                                                |

|-----|------|-------------------------|----------------------------------------------------------------------------|

| 7   | 1    | SRC[T/C]3               | Output enable for SRC3<br>0 = Output Disabled, 1 = Output Enabled          |

| 6   | 1    | SRC[T/C]2/SATA          | Output enable for SRC2/SATA<br>0 = Output Disabled, 1 = Output Enabled     |

| 5   | 1    | SRC[T/C]1/LCD_100M[T/C] | Output enable for SRC1/LCD_100M<br>0 = Output Disabled, 1 = Output Enabled |

| 4   | 1    | SRC[T/C]0/DOT96[T/C]    | Output enable for SRC0/DOT96<br>0 = Output Disabled, 1 = Output Enabled    |

| 3   | 1    | CPU[T/C]1               | Output enable for CPU1<br>0 = Output Disabled, 1 = Output Enabled          |

| 2   | 1    | CPU[T/C]0               | Output enable for CPU0<br>0 = Output Disabled, 1 = Output Enabled          |

| 1   | 1    | PLL1_SS_EN              | Enable PLL1s spread modulation,<br>0 = Spread Disabled, 1 = Spread Enabled |

| 0   | 1    | PLL3_SS_EN              | Enable PLL3s spread modulation 0 = Spread Disabled, 1 = Spread Enabled     |

#### Byte 5: Control Register 5

| Bit | @Pup | Name      | Description                                                                                              |

|-----|------|-----------|----------------------------------------------------------------------------------------------------------|

| 7   | 0    | CR#_A_EN  | Enable CR#_A (clk req) 0 = Disabled, 1 = Enabled,                                                        |

| 6   | 0    | CR#_A_SEL | Set $CR\#_A \rightarrow SRC0$ or $SRC2$<br>0 = $CR\#_A \rightarrow SRC0$ , 1 = $CR\#_A \rightarrow SRC2$ |

| 5   | 0    | CR#_B_EN  | Enable CR#_B(clk req) 0 = Disabled, 1 = Enabled,                                                         |

| 4   | 0    | CR#_B_SEL | Set CR#_B $\rightarrow$ SRC1 or SRC4<br>0 = CR#_B $\rightarrow$ SRC1, 1 = CR#_B $\rightarrow$ SRC4       |

| 3   | 0    | CR#_C_EN  | Enable CR#_C (clk req) 0 = Disabled, 1 = Enabled                                                         |

| 2   | 0    | CR#_C_SEL | Set $CR\#_C \rightarrow SRC0$ or $SRC2$<br>0 = $CR\#_C \rightarrow SRC0$ , 1 = $CR\#_C \rightarrow SRC2$ |

| 1   | 0    | CR#_D_EN  | Enable CR#_D (clk req) 0 = Disabled, 1 = Enabled                                                         |

| 0   | 0    | CR#_D_SEL | Set $CR\#_D \rightarrow SRC1$ or $SRC4$<br>0 = $CR\#_D \rightarrow SRC1$ , 1 = $CR\#_D \rightarrow SRC4$ |

## Byte 6: Control Register 6

| Bit | @Pup | Name             | Description                                                                 |

|-----|------|------------------|-----------------------------------------------------------------------------|

| 7   | 0    | CR#_E_EN         | Enable CR#_E (clk req) → SRC6<br>0 = Disabled, 1 = Enabled                  |

| 6   | 0    | CR#_F_EN         | Enable CR#_F (clk req) → SRC8<br>0 = Disabled, 1 = Enabled                  |

| 5   | 0    | CR#_G_EN         | Enable CR#_G (clk req) → SRC9<br>0 = Disabled, 1 = Enabled                  |

| 4   | 0    | CR#_H_EN         | Enable CR#_H (clk req) → SRC10<br>0 = Disabled, 1 = Enabled                 |

| 3   | 0    | Reserved         | Reserved                                                                    |

| 2   | 0    | Reserved         | Reserved                                                                    |

| 1   | 0    | LCD_100_STP_CTRL | If set, LCD_100 stop with PCI_STP# 0 = Free running, 1 = PCI_STP# stoppable |

| 0   | 0    | SRC_STP_CTRL     | If set, SRCs stop with PCI_STP#  0 = Free running, 1 = PCI_STP# stoppable   |

## Byte 7: Vendor ID

| Bit | @Pup | Name            | Description         |

|-----|------|-----------------|---------------------|

| 7   | 0    | Rev Code Bit 3  | Revision Code Bit 3 |

| 6   | 0    | Rev Code Bit 2  | Revision Code Bit 2 |

| 5   | 0    | Rev Code Bit 1  | Revision Code Bit 1 |

| 4   | 1    | Rev Code Bit 0  | Revision Code Bit 0 |

| 3   | 1    | Vendor ID bit 3 | Vendor ID Bit 3     |

| 2   | 0    | Vendor ID bit 2 | Vendor ID Bit 2     |

| 1   | 0    | Vendor ID bit 1 | Vendor ID Bit 1     |

| 0   | 0    | Vendor ID bit 0 | Vendor ID Bit 0     |

## Byte 8: Control Register 8

| Bit | @Pup | Name       | Description                                                                                                                                                                                                                                                                                                                                           |

|-----|------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | 1    | Device_ID3 | 0000 = CK505 Yellow Cover Device, 56-pin TSSOP                                                                                                                                                                                                                                                                                                        |

| 6   | 0    | Device_ID2 | 70001 = CK505 Yellow Cover Device, 64-pin TSSOP<br>20010 = CK505 Yellow Cover Device, 48-pin QFN (Reserved)                                                                                                                                                                                                                                           |

| 5   | 0    | Device_ID1 | 0011 = CK505 Yellow Cover Device, 56-pin QFN (Reserved)                                                                                                                                                                                                                                                                                               |

| 4   | 0    | Device_ID0 | 0100 = CK505 Yellow Cover Device, 64-pin QFN 0101 = CK505 Yellow Cover Device, 72-pin QFN (Reserved) 0110 = CK505 Yellow Cover Device, 48-pin SSOP (Reserved) 0111 = CK505 Yellow Cover Device, 48-pin SSOP (Reserved) 1000 = Reserved 1001 = CY28548 1010 = Reserved 1011 = Reserved 1100 = Reserved 1110 = Reserved 1111 = Reserved 1111 = Reserved |

| 3   | 0    | Reserved   | Reserved                                                                                                                                                                                                                                                                                                                                              |

| 2   | 0    | Reserved   | Reserved                                                                                                                                                                                                                                                                                                                                              |

| 1   | 1    | 27M_NSS_OE | Output enable for 27M_NSS 0 = Output Disabled, 1 = Output Enabled                                                                                                                                                                                                                                                                                     |

| 0   | 1    | 27M_SS_OE  | Output enable for 27M_SS 0 = Output Disabled, 1 = Output Enabled                                                                                                                                                                                                                                                                                      |

#### Byte 9: Control Register 9

| Bit | @Pup | Name                 | Description                                                                                                                    |

|-----|------|----------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 7   | 0    | PCIF_0_with PCI_STP# | Allows control of PCIF_0 with assertion of PCI_STP# 0 = Free running PCIF, 1 = Stopped with PCI_STP#                           |

| 6   | HW   | TME_STRAP            | Trusted mode enable strap status 0 = Normal, 1 = No overclocking                                                               |

| 5   | 1    | REF_DSC1             | REF drive strength 1 of 2 (See Byte 17 and 18 for more setting) 0 = Low, 1 = High                                              |

| 4   | 0    | TEST_MODE_SEL        | Mode select either REF/N or tri-state 0 = All output tri-state, 1 = All output REF/N                                           |

| 3   | 0    | TEST_MODE_ENTRY      | Allow entry into test mode 0 = Normal operation, 1 = Enter test mode                                                           |

| 2   | 1    | I2C_VOUT<2>          | Differential Amplitude Configuration                                                                                           |

| 1   | 0    | I2C_VOUT<1>          | I2C_VOUT[2,1,0]                                                                                                                |

| 0   | 1    | I2C_VOUT<0>          | 000 = 0.63V<br>001 = 0.71V<br>010 = 0.77V<br>011 = 082V<br>100 = 0.86V<br>101 = 0.90V (default)<br>110 = 0.93V<br>111 = unused |

## Byte 10: Control Register 10

| Bit | @Pup | Name           | Description                                                      |

|-----|------|----------------|------------------------------------------------------------------|

| 7   | HW   | GCLK_SEL latch | Readback of GCLK_SEL latch<br>0 = DOT96/LCD_100, 1 = SRC0/27 MHz |

| 6   | 1    | PLL3_EN        | PLL3 power down 0 = Power down, 1 = Power up                     |

...... DOC #: SP-AP-0063 (Rev. AA) Page 12 of 31

## Byte 10: Control Register 10 (continued)

| Bit | @Pup | Name             | Description                                                    |  |  |  |

|-----|------|------------------|----------------------------------------------------------------|--|--|--|

| 5   | 1    | PLL2_EN          | PLL2 power down 0 = Power down, 1 = Power up                   |  |  |  |

| 4   | 1    | SRC_DIV_EN       | SRC divider disable<br>0 = Disabled, 1 = Enabled               |  |  |  |

| 3   | 1    | PCI_DIV_EN       | PCI divider disable 0 = Disabled, 1 = Enabled                  |  |  |  |

| 2   | 1    | CPU_DIV_EN       | CPU divider disable<br>0 = Disabled, 1 = Enabled               |  |  |  |

| 1   | 1    | CPU1 Stop Enable | Enable CPU_STP# control of CPU1 0 = Free running, 1= Stoppable |  |  |  |

| 0   | 1    | CPU0 Stop Enable | Enable CPU_STP# control of CPU0 0 = Free running, 1= Stoppable |  |  |  |

#### Byte 11: Control Register 11

| Bit | @Pup | Name     | Description |

|-----|------|----------|-------------|

| 7   | 0    | Reserved | Reserved    |

| 6   | 0    | Reserved | Reserved    |

| 5   | 0    | Reserved | Reserved    |

| 4   | 0    | Reserved | Reserved    |

| 3   | 0    | Reserved | Reserved    |

| 2   | 0    | Reserved | Reserved    |

| 1   | 0    | Reserved | Reserved    |

| 0   | 0    | Reserved | Reserved    |

## Byte 12: Byte Count

| Bit | @Pup | Name     | Description                                                                                                     |

|-----|------|----------|-----------------------------------------------------------------------------------------------------------------|

| 7   | 0    | Reserved | Reserved                                                                                                        |

| 6   | 0    | Reserved | Reserved                                                                                                        |

| 5   | 0    | BC5      | Byte count register for block read operation.                                                                   |

| 4   | 1    | BC4      | The default value for Byte count is 19.  In order to read beyond Byte 19, the user should change the byte count |

| 3   | 0    | BC3      | limit.to or beyond the byte that is desired to be read.                                                         |

| 2   | 0    | BC2      |                                                                                                                 |

| 1   | 1    | BC1      |                                                                                                                 |

| 0   | 1    | BC0      |                                                                                                                 |

#### Byte 13: Control Register 13

| Bit | @Pup | Name           | Description                                                                                  |  |  |  |

|-----|------|----------------|----------------------------------------------------------------------------------------------|--|--|--|

| 7   | 1    | USB_BIT1       | USB drive strength 1 of 3(See Byte 17 for more setting) 0 = Low, 1= High                     |  |  |  |

| 6   | 1    | PCI/ PCIF_BIT1 | PCI drive strength 1 of 3(See Byte 17 & 18 for more setting) 0 = Low, 1 = High               |  |  |  |

| 5   | 0    | PLL1_Spread    | Select percentage of spread for PLL1 0 = 0.5%, 1=1%                                          |  |  |  |

| 4   | 1    | SATA_SS_EN     | Enable SATA spread modulation,<br>0 = Spread Disabled, 1 = Spread Enabled                    |  |  |  |

| 3   | 1    | CPU[T/C]2      | Allow control of CPU2 with assertion of CPU_STP# 0 = Free running, 1 = Stopped with CPU_STP# |  |  |  |

## Byte 13: Control Register 13 (continued)

| Bit | @Pup | Name          | Description                                                                                                                                                                                                                                                                                                                 |  |

|-----|------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2   | 1    | SE1/SE2_BIT_1 | SE1 and SE2 Drive Strength Setting 1 of 3 (See Byte 17 and 18 for more se 0 = Low, 1= High                                                                                                                                                                                                                                  |  |

| 1   | 1    | Reserved      | Reserved                                                                                                                                                                                                                                                                                                                    |  |

| 0   | 1    | SW_PCI        | SW PCI_STP# Function 0 = SW PCI_STP assert, 1 = SW PCI_STP deassert When this bit is set to 0, all STOPPABLE PCI, PCIF and SRC outputs are stopped in a synchronous manner with no short pulses. When this bit is set to 1, all STOPPED PCI, PCIF and SRC outputs are resumed in a synchronous manner with no short pulses. |  |

#### Byte 14: Control Register 14

| Bit | @Pup | Name       | Description                                                        |

|-----|------|------------|--------------------------------------------------------------------|

| 7   | 0    | CPU_DAF_N7 | If Prog_CPU_EN is set, the values programmed in CPU_DAF_N[8:0] and |

| 6   | 0    | CPU_DAF_N6 | CPU_DAF_M[6:0] are used to determine the CPU output frequency.     |

| 5   | 0    | CPU_DAF_N5 |                                                                    |

| 4   | 0    | CPU_DAF_N4 |                                                                    |

| 3   | 0    | CPU_DAF_N3 |                                                                    |

| 2   | 0    | CPU_DAF_N2 |                                                                    |

| 1   | 0    | CPU_DAF_N1 |                                                                    |

| 0   | 0    | CPU_DAF_N0 |                                                                    |

## Byte 15: Control Register 15

| Bit | @Pup | Name       | Description                                                        |  |  |  |  |

|-----|------|------------|--------------------------------------------------------------------|--|--|--|--|

| 7   | 0    | CPU_DAF_N8 | See Byte 14 for description                                        |  |  |  |  |

| 6   | 0    | CPU_DAF_M6 | If Prog_CPU_EN is set, the values programmed in CPU_DAF_N[8:0] and |  |  |  |  |

| 5   | 0    | CPU_DAF_M5 | CPU_DAF_M[6:0] are used to determine the CPU output frequency.     |  |  |  |  |

| 4   | 0    | CPU_DAF_M4 |                                                                    |  |  |  |  |

| 3   | 0    | CPU_DAF_M3 |                                                                    |  |  |  |  |

| 2   | 0    | CPU_DAF_M2 |                                                                    |  |  |  |  |

| 1   | 0    | CPU_DAF_M1 |                                                                    |  |  |  |  |

| 0   | 0    | CPU_DAF_M0 |                                                                    |  |  |  |  |

## Byte 16: Control Register 16

| Bit | @Pup | Name     | Description                    |  |  |  |

|-----|------|----------|--------------------------------|--|--|--|

| 7   | 0    | PCI-E_N7 | PCI-E Dial-A-Frequency® Bit N7 |  |  |  |

| 6   | 0    | PCI-E_N6 | PCI-E Dial-A-Frequency Bit N6  |  |  |  |

| 5   | 0    | PCI-E_N5 | PCI-E Dial-A-Frequency Bit N5  |  |  |  |

| 4   | 0    | PCI-E_N4 | PCI-E Dial-A-Frequency Bit N4  |  |  |  |

| 3   | 0    | PCI-E_N3 | PCI-E Dial-A-Frequency Bit N3  |  |  |  |

| 2   | 0    | PCI-E_N2 | PCI-E Dial-A-Frequency Bit N2  |  |  |  |

| 1   | 0    | PCI-E_N1 | PCI-E Dial-A-Frequency Bit N1  |  |  |  |

| 0   | 0    | PCI-E_N0 | PCI-E Dial-A-Frequency Bit N0  |  |  |  |

#### Byte 17: Control Register 17

| Bit | @Pup | Name           | Description                                                                               |  |  |  |

|-----|------|----------------|-------------------------------------------------------------------------------------------|--|--|--|

| 7   | 0    | SMSW_EN        | Enable Smooth Switching<br>0 = Disabled, 1= Enabled                                       |  |  |  |

| 6   | 0    | SMSW_SEL       | Smooth switch select 0 = CPU_PLL, 1 = SRC_PLL                                             |  |  |  |

| 5   | 0    | SE1/SE2_BIT0   | SE1 and SE2 drive strength Setting 2 of 3(see Byte 18 for more setting) 0 = Low, 1= High  |  |  |  |

| 4   | 0    | Prog_PCI-E_EN  | Programmable PCI-E frequency enable 0 = Disabled, 1= Enabled                              |  |  |  |

| 3   | 0    | Prog_CPU_EN    | Programmable CPU frequency enable 0 = Disabled, 1= Enabled                                |  |  |  |

| 2   | 0    | REF_BIT0       | REFdrive strength strength Setting 2 of 3(see Byte 18 for more setting) 0 = Low, 1= High  |  |  |  |

| 1   | 0    | USB_BIT0       | USB drive strength strength Setting 2 of 3(see Byte 18 for more setting) 0 = Low, 1= High |  |  |  |

| 0   | 0    | PCI/ PCIF_BIT0 | PCI drive strength strength Setting 2 of 3(see Byte 18 for more setting) 0 = Low, 1= High |  |  |  |

#### Byte 18: Control Register 18

| 7 | 0 | REF_BIT2      | Drive Strength Co | ontrol   |                          |           |                    |

|---|---|---------------|-------------------|----------|--------------------------|-----------|--------------------|

| 6 | 0 | RESERVED      |                   |          |                          |           |                    |

| 5 | 1 | RESERVED      |                   |          |                          |           |                    |

| 4 | 0 | RESERVED      |                   | BIT_2    | BIT_1<br>(Various Bytes) | BIT_0     | Buffer<br>Strength |

| 3 | 0 | USB_BIT2      |                   | (Byte18) | (valious Bytes)          | (Byte 17) | Strongest          |

| 2 | 0 | PCI/PCIF_BIT2 |                   | 1        | 1                        | 0         | <b>A</b>           |

| 1 | 0 | SE1/SE2_BIT2  |                   | 1        | 0                        | 1         | 1 [                |

| 0 | 0 | RESERVED      |                   | 1        | 0                        | 0         |                    |

|   |   |               |                   | 0        | 1                        | 1         |                    |

|   |   |               | Default           | 0        | 1                        | 0         |                    |

|   |   |               |                   | 0        | 0                        | 1         | 1                  |

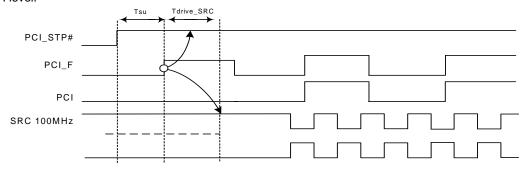

#### Table 5. Output Driver Status during PCI-STP# and CPU-STP#

|                     |                      | PCI_STP# Asserted | CPU_STP# Asserted  | SMBus OE Disabled       |

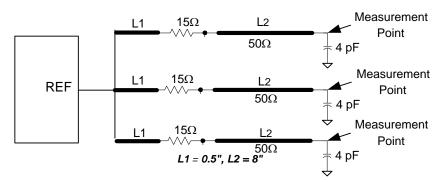

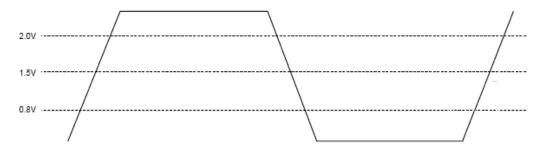

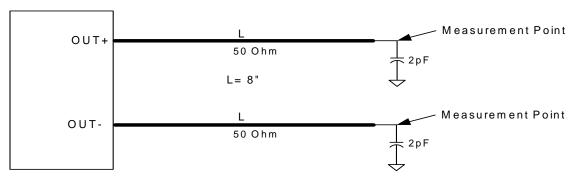

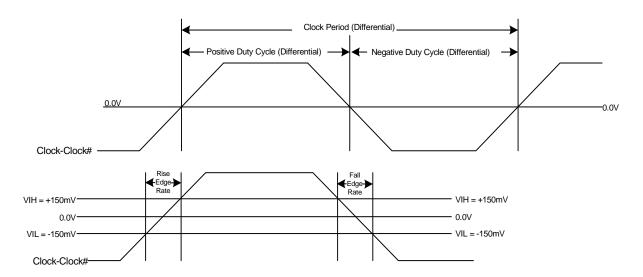

|---------------------|----------------------|-------------------|--------------------|-------------------------|